# Mentor Graphics Introduction to VHDL

July 1994

Copyright © 1991-1994 Mentor Graphics Corporation. All rights reserved.

Confidential. May be photocopied by licensed customers of

Mentor Graphics for internal business purposes only.

The software programs described in this document are confidential and proprietary products of Mentor Graphics Corporation (Mentor Graphics) or its licensors. No part of this document may be photocopied, reproduced or translated, or transferred, disclosed or otherwise provided to third parties, without the prior written consent of Mentor Graphics.

The document is for informational and instructional purposes. Mentor Graphics reserves the right to make changes in specifications and other information contained in this publication without prior notice, and the reader should, in all cases, consult Mentor Graphics to determine whether any changes have been made.

The terms and conditions governing the sale and licensing of Mentor Graphics products are set forth in the written contracts between Mentor Graphics and its customers. No representation or other affirmation of fact contained in this publication shall be deemed to be a warranty or give rise to any liability of Mentor Graphics whatsoever.

MENTOR GRAPHICS MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OR MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

MENTOR GRAPHICS SHALL NOT BE LIABLE FOR ANY INCIDENTAL, INDIRECT, SPECIAL, OR CONSEQUENTIAL DAMAGES WHATSOEVER (INCLUDING BUT NOT LIMITED TO LOST PROFITS) ARISING OUT OF OR RELATED TO THIS PUBLICATION OR THE INFORMATION CONTAINED IN IT, EVEN IF MENTOR GRAPHICS CORPORATION HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Portions of this manual are based on IEEE Std 1076-1987, *IEEE Standard VHDL Language Reference Manual*, copyright ©1988 by the Institute of Electrical and Electronics Engineers, Inc. The IEEE does not, in whole or in part, endorse the contents of this manual. For information on purchasing the IEEE Standard, call 1-800-678-IEEE.

**RESTRICTED RIGHTS LEGEND** Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subdivision (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

A complete list of trademark names appears in a separate "Trademark Information" document.

#### **Mentor Graphics Corporation**

8005 S.W. Boeckman Road, Wilsonville, Oregon 97070.

Copyright © Mentor Graphics Corporation 1993. All rights reserved.

An unpublished work of Mentor Graphics Corporation.

### **TABLE OF CONTENTS**

| About This Manual                                  | xi   |

|----------------------------------------------------|------|

| Section 1                                          |      |

| Overview                                           | 1-1  |

| General VHDL Modeling Principles                   | 1-3  |

| Top-Down Design                                    |      |

| Modularity                                         | 1-4  |

| Abstraction                                        |      |

| Information Hiding                                 |      |

| Uniformity                                         |      |

| Summary                                            | 1-11 |

| Section 2                                          |      |

| VHDL Fundamentals                                  | 2-1  |

| VHDL Building Blocks                               | 2-2  |

| Major Language Constructs                          | 2-3  |

| Primary Language Abstraction                       |      |

| Design Description Methods                         | 2-10 |

| Structural Description                             |      |

| Behavioral Description                             |      |

| Structural and Behavioral Description Summary      |      |

| Data-Flow Description                              | 2-30 |

| Constructs Found in Each Design Description Method | 2-34 |

| Section 3                                          |      |

| Foundation for Declaring ObjectsTypes              | 3-1  |

| Various Classes of Type Definitions                |      |

| Scalar Types                                       | 3-4  |

| Mentor Graphics Introduction to VHDL, July 1994    | iii  |

# **TABLE OF CONTENTS** [continued]

| <b>Section 3</b> Fe | oundation | for Decla | ring Objects- | Types | [continued] |

|---------------------|-----------|-----------|---------------|-------|-------------|

|---------------------|-----------|-----------|---------------|-------|-------------|

| Physical Types                                              | _ 3-4 |

|-------------------------------------------------------------|-------|

| Floating Point Types                                        | _ 3-6 |

| Enumeration Types                                           | _ 3-7 |

| Integer Types                                               |       |

| Composite Types                                             |       |

| Array Types                                                 |       |

| Record Types                                                |       |

| File Types                                                  |       |

| Access Types                                                |       |

| Retrieving Information on Certain Kinds of Objects          |       |

|                                                             |       |

| Section 4                                                   |       |

|                                                             |       |

| Constructs for Decomposing Design Functionality             | _ 4-1 |

| Concurrent Decomposition                                    | _ 4-3 |

| Block Statement                                             |       |

| Component Instantiation                                     |       |

| Sequential Decomposition                                    |       |

| SubprogramsFunctions and Procedures                         |       |

| Function Call                                               |       |

| Procedure Call                                              |       |

| Contrasting Concurrent and Sequential Modeling              |       |

| How Values Get Assigned to Signals and Variables            |       |

| Resolving a Signal Value When Driven by Multiple Assignment | -     |

| Statements                                                  | 4-47  |

| Creating Shared ModulesPackages                             |       |

| Making a Package VisibleLibrary Clause and Use Clause       | 4-48  |

# **TABLE OF CONTENTS** [continued]

| <b>Section</b> | 5                      |

|----------------|------------------------|

| occuon         | $\mathbf{\mathcal{L}}$ |

| Global Considerations                                   | 5-1        |

|---------------------------------------------------------|------------|

| Scope and Visibility                                    | 5-1        |

| Reusing Predefined NamesOverloading                     | 5-0        |

| Overloading Enumeration Literals                        |            |

| Overloading Subprograms                                 |            |

| Overloading Operators                                   |            |

| - Tributing operators                                   | 0 1        |

|                                                         |            |

| Section 6                                               |            |

|                                                         |            |

| Coding Techniques                                       | 6-1        |

|                                                         |            |

| General VHDL Coding Guidelines                          |            |

| Various Techniques for Modeling Timing                  | 6-3        |

| Embedding Fixed-Delay Parameters Within a Model         |            |

| Embedding Variable-Delay Parameters Within a Model      |            |

| Using Generics to Parameterize a Model                  |            |

| Parameterizing Rise/Fall Delays with Generics           |            |

| Increasing Model Accuracy with Error Checking           | 6-17       |

| Modeling for Increased Simulation Performance           | 6-23       |

| When to Use Variables Within a Loop Instead of Signals  | 6-23       |

| Using Resolution Functions Only When Needed             | 6-25       |

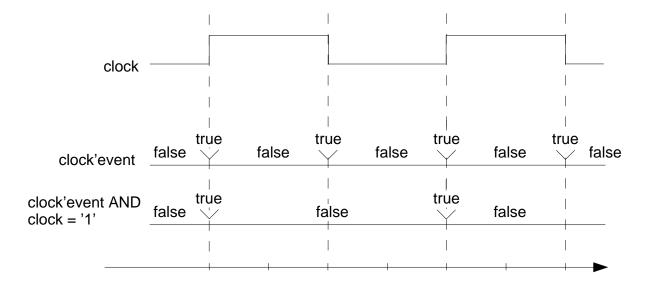

| Using Attribute 'event Instead of 'stable When Possible |            |

| Creating Lookup Tables for Logic Operations             |            |

| Process StatementsAvoiding Infinite Loops               |            |

| Using VHDL for Simulation Stimulus                      |            |

|                                                         |            |

|                                                         |            |

| Glossary                                                | Glossary-1 |

|                                                         | •          |

### **Index**

# **LIST OF FIGURES**

| 1-1. Various Things You Can Describe with VHDL        | 1-2                 |

|-------------------------------------------------------|---------------------|

| 1-2. Flat-Level Partitioning of a Hardware Design _   | 1-5                 |

| 1-3. A Hardware Module Created from VHDL Build        | ing Blocks 1-6      |

| 1-4. Hierarchical Partioning of a VHDL Shifter Desc   | ription 1-7         |

| 1-5. Applying Abstraction to a ROM Description        |                     |

| 1-6. Hiding Unessential Details of NAND Gate Leve     | 1 1-10              |

| 2-1. Port Clause Syntax Diagram                       | 2-2                 |

| 2-2. Major Language Construct Hierarchy               | 2-4                 |

| 2-3. Entity Name Usage in Entity Declaration and Ar   | chitecture          |

| Body                                                  | 2-7                 |

| 2-4. Multiple Architecture Bodies for One Entity Dec  | claration 2-9       |

| 2-5. Symbol Representation of Two-Input Multiplexe    | er 2-11             |

| 2-6. A Schematic Editor Hierarchical Design of a Mu   | ıltiplexer 2-11     |

| 2-7. Gate-Level Representation of Two-Input Multip    | lexer 2-12          |

| 2-8. Code of Structural Description for a Multiplexer |                     |

| 2-9. Two-Input Multiplexer with Associated Structur   | al Description 2-14 |

| 2-10. Code of Behavioral Description for a Multiplex  | xer 2-15            |

| 2-11. Code Example of Behavioral Description for a    | Shifter 2-19        |

| 2-12. Arrays Represented as Data-Storage Containers   | s 2-20              |

| 2-13. Variable Assignment for SHFTOUT Array After     | er 10 ns 2-21       |

| 2-14. Variable Assignment for Array When SHFTCT       | TL = 00 2-23        |

| 2-15. Variable Assignment for Array When SHFTCT       | TL = 01 2-23        |

| 2-16. Variable Assignment for Array When SHFTCT       | TL = 10 2-24        |

| 2-17. Variable Assignment for Array When SHFTCT       | TL = 11 2-25        |

| 2-18. Four-Bit Shifter Waveforms                      | 2-27                |

| 2-19. Schematic for a Four-Bit Shifter                | 2-27                |

| 2-20. Comparing Structural and Behavioral Descripti   |                     |

| 2-21. Example of Data-Flow Description for a Multip   |                     |

| 2-22. Comparison of Behavioral and Data-Flow Shift    |                     |

| Descriptions                                          | 2-33                |

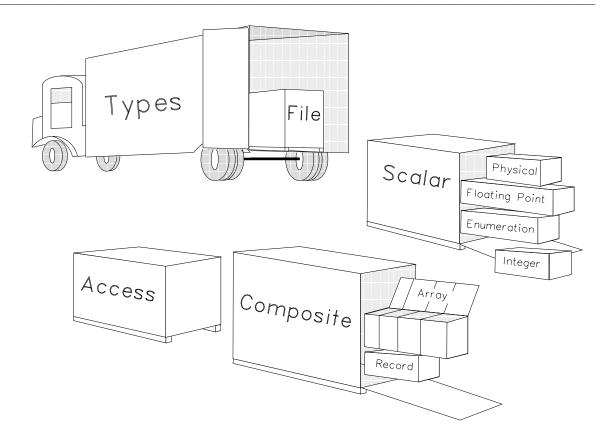

| 3-1. Various Classes of Type Definitions Within a Ty  | ype                 |

| Declaration                                           | 3-3                 |

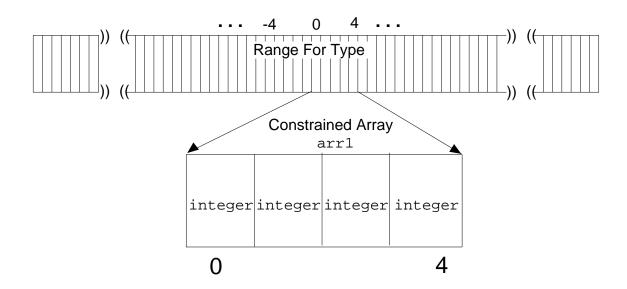

| 3-2. Defining a Constrained Array Type                | 3-10                |

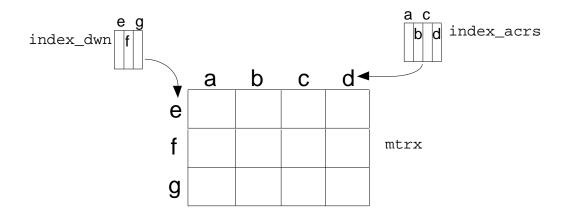

| 3-3. Defining a Constrained Array Matrix              |                     |

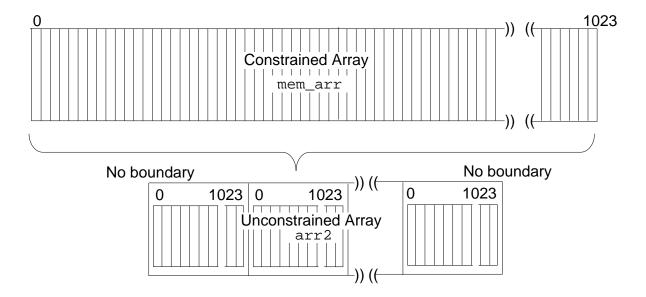

| 3-4. Defining an Unconstrained Array with Array Ele   |                     |

| 3-5. Signal Attribute Example                         |                     |

| 4-1. Concurrent and Sequential Operations             |                     |

| 4-2. Relating Blocks to the VHDL Hierarchy            |                     |

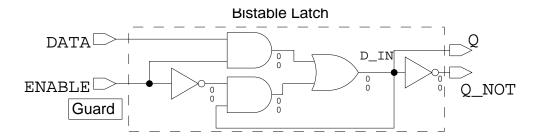

| 4-3. Using the Guard Expression on a Bistable Latch   | 4-6                 |

# LIST OF FIGURES [continued]

| 4-4. Instantiating an AND Gate in a MUX Description       | 4-10         |

|-----------------------------------------------------------|--------------|

| 4-5. Instantiating a Component Using Different Parameters |              |

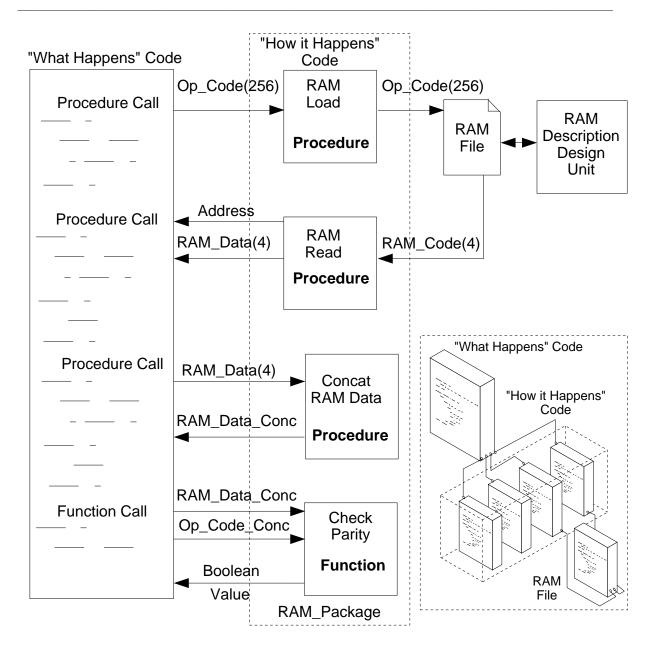

| 4-6. Using Procedures and Functions                       | 4-16         |

| 4-7. Code Example of a SubprogramRAM Load Procedur        | re 4-17      |

| 4-8. Code Example of a SubprogramRAM Read Procedur        |              |

| 4-9. Example of a SubprogramConcatenate Data Procedu      |              |

| 4-10. Code Example of a SubprogramParity Checker Fun      |              |

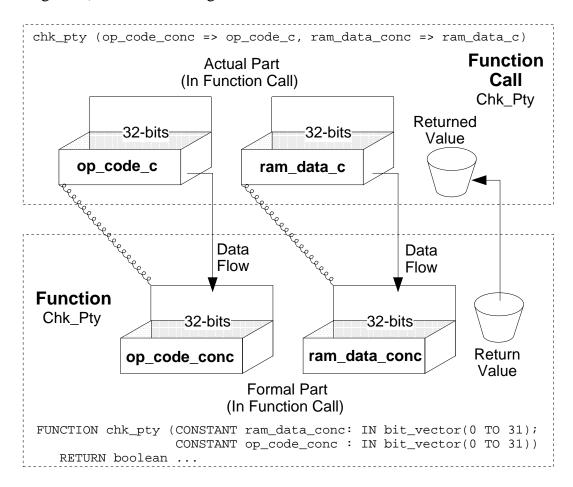

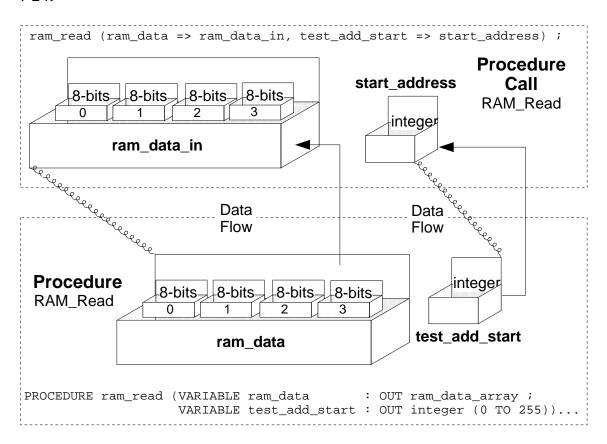

| 4-11. Associating Actual Parameters to Formal Parameters  |              |

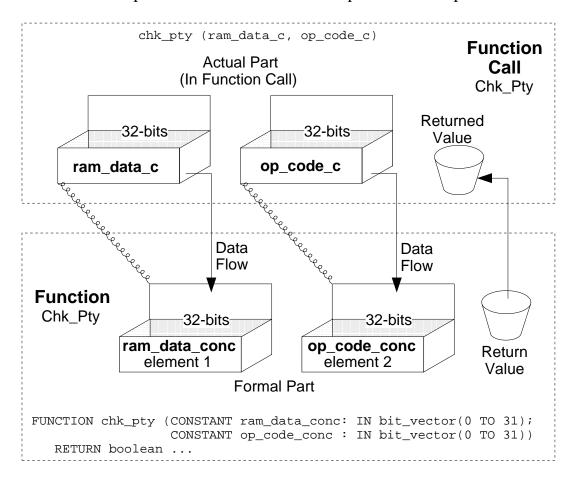

| 4-12. Positional Parameter Notation in a Function Call    | 4-26         |

| 4-13. Procedure Call Parameter Association                | 4-28         |

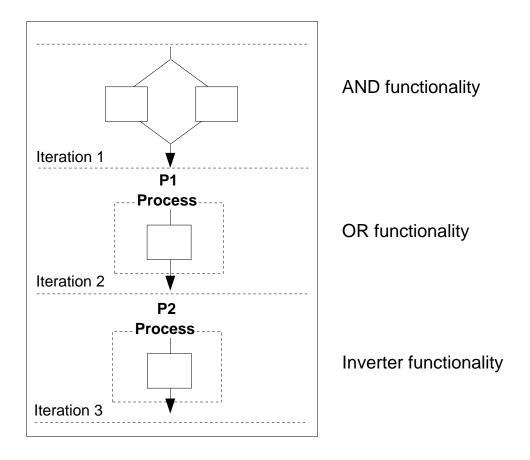

| 4-14. Evaluation Flow for First Behavioral AOI Models     | 4-32         |

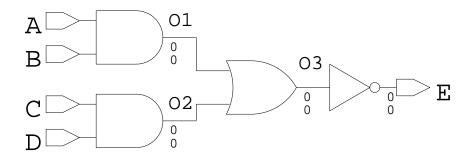

| 4-15. AND/OR/Inverter Circuit                             | 4-34         |

| 4-16. Operation-Flow Diagram for AOI Circuit              | 4-35         |

| 4-17. Changing Model Behavior by Moving Sequential Sta    | tements 4-38 |

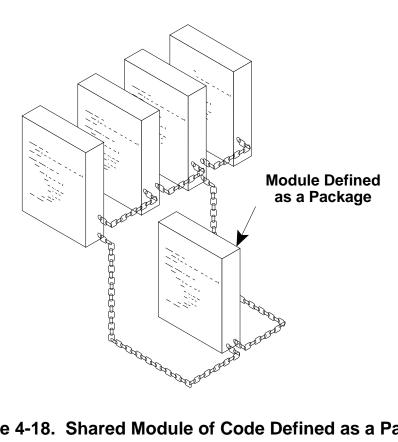

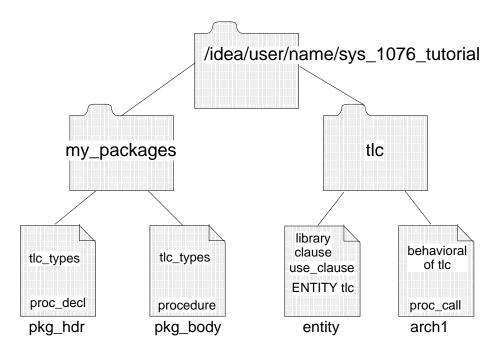

| 4-18. Shared Module of Code Defined as a Package          |              |

| 4-19. Portion of Code from a Package Called Standard      | 4-45         |

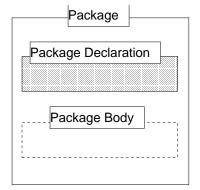

| 4-20. Effects on Entity and Architecture When Changing P. | ackage       |

| Header                                                    | 4-47         |

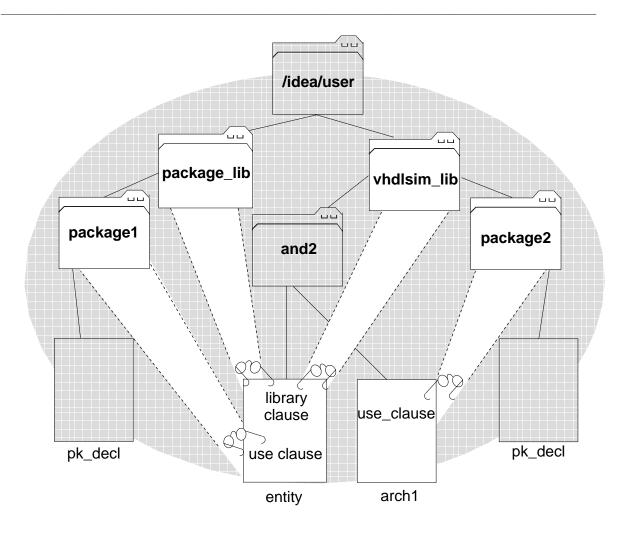

| 4-21. Making Packages Visible with Library and Use Claus  | ses 4-49     |

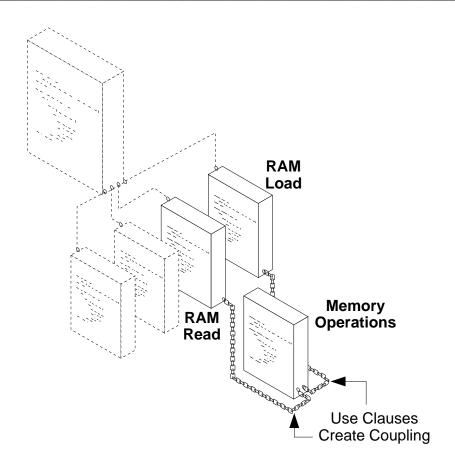

| 4-22. Coupling Two Procedures to One Package with Use O   |              |

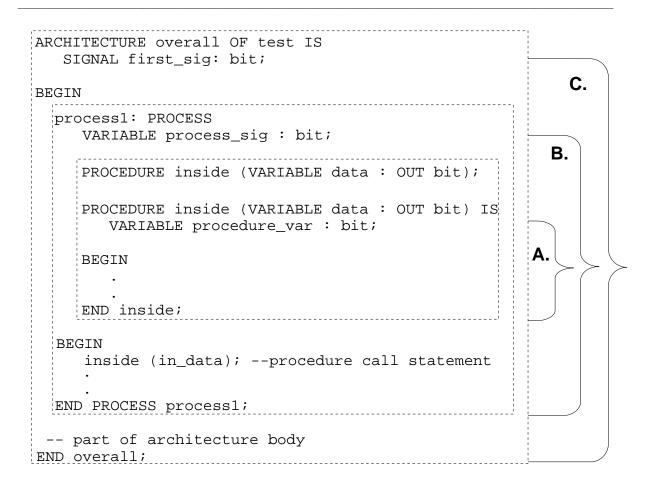

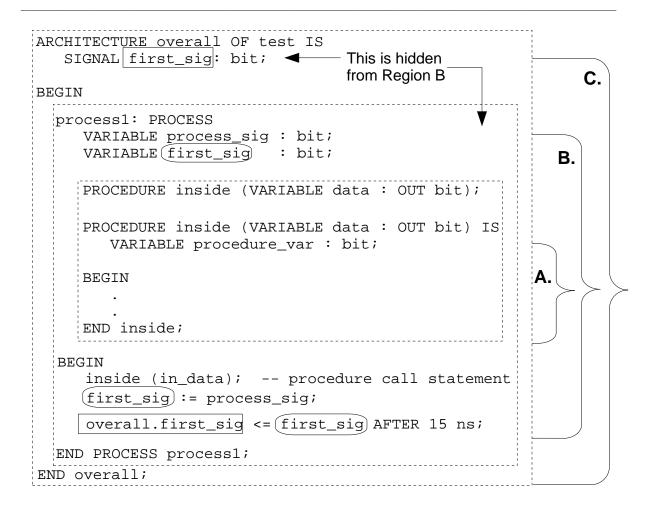

| 5-1. Example of Scope and Visibility                      |              |

| - · · · · · · · · · · · · · · · · · · ·                   | 5-5          |

| 5-3. Overloading Enumeration Literals                     | 5-7          |

| 5-4. Overloading SubprogramsFunctions                     | 5-9          |

| 5-5. Calling a Specific Overloaded SubprogramFunction     | 5-10         |

| 5-6. Overloading Operators                                | 5-12         |

| 5-7. Calling a Specific Overloaded Operator               | 5-13         |

| 6-1. Good Presentation Style for Shifter Description      | 6-4          |

| 6-2. Poor Presentation Style for Shifter Description      | 6-5          |

| 6-3. Embedding Variable-Delay Parameters Within Model     | 6-7          |

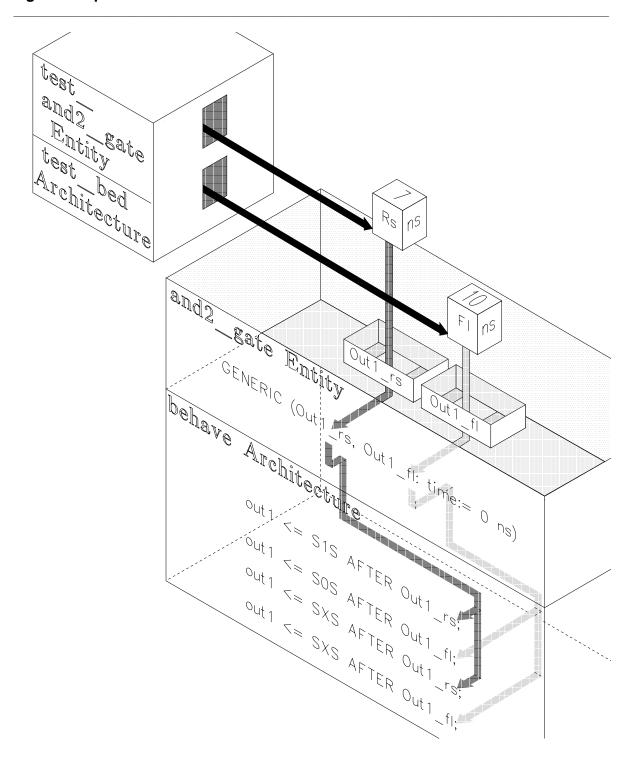

| 6-4. Test Bed Code for AND Gate Model                     | 6-8          |

| 6-5. AND Gate Model Using Generics to Receive Timing      |              |

| Parameters                                                | 6-10         |

| 6-6. Using Generics to Pass Customized Parameters to a M  | odel6-11     |

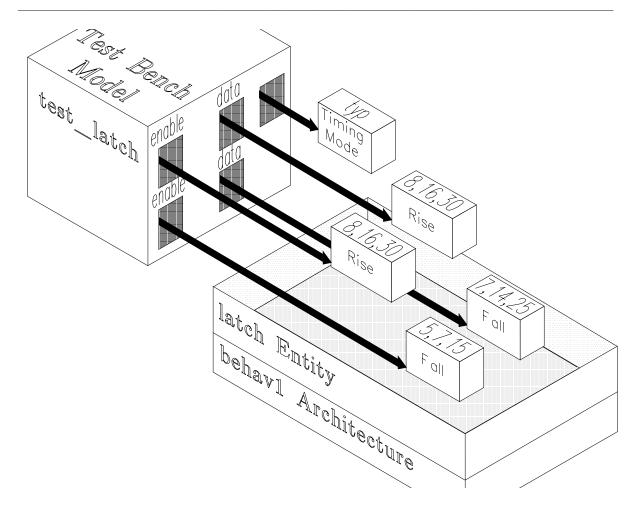

| 6-7. Entity for One-Bit Latch Using Parameterized Rise/Fa |              |

| Delays                                                    | 6-13         |

| 6-8. Rise/Fall Values Passed to One-Bit Latch Model       | 6-14         |

| 6-9. Test Bed Code for Latch Model                        | 6-15         |

# LIST OF FIGURES [continued]

| 6-10. | Architecture Body for One-Bit Latch with Parameterized |      |

|-------|--------------------------------------------------------|------|

| Del   | lays                                                   | 6-16 |

| 6-11. | Error-Checking Code Added to Entity for One-Bit Latch  | 6-18 |

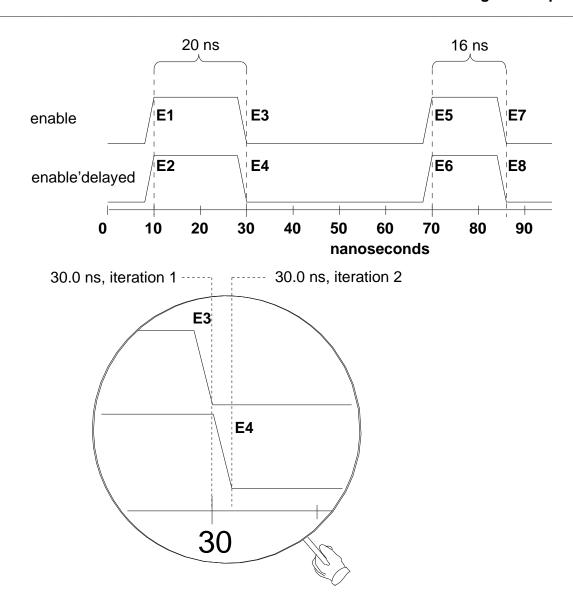

| 6-12. | Comparing a Signal with Its Delayed Counterpart        | 6-20 |

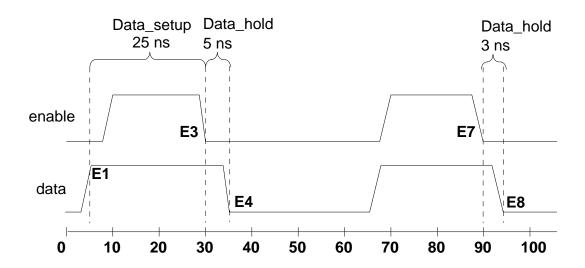

| 6-13. | Setup/Hold Timing for Latch                            | 6-22 |

| 6-14. | Signal Assignment Within a Loop                        | 6-24 |

| 6-15. | Logic Example Package                                  | 6-28 |

| 6-16. | Correcting an Infinite Loop in a Process Statement     | 6-30 |

| 6-17. | Wait Statement in a Procedure Avoids an Infinite Loop  | 6-31 |

| 6-18. | VHDL Model Used as Stimulus for AND Gate               | 6-33 |

# **LIST OF TABLES**

| 4-1. | AND/OR/INVERT Truth Table                   | 4-29 |

|------|---------------------------------------------|------|

| 4-2. | AND/OR/Invert Karnaugh Map                  | 4-30 |

| 5-1. | Operators by Precedence                     | 5-11 |

| 6-1. | Constant Values Set in Latch Test Bed Model | 6-17 |

### **Table of Contents**

# **About This Manual**

This manual introduces some of the language concepts and provides some general coding techniques for the modeling language based on IEEE Std 1076-1987, *IEEE Standard VHDL Language Reference Manual*.

# **Manual Organization**

This manual is organized into the following sections:

- Section 1, "Overview," provides an introduction to VHDL and a description of the modeling principles supported by the language.

- Section 2, "VHDL Fundamentals," introduces basic VHDL concepts and defines many of the terms associated with the language.

- Section 3, "Foundation for Declaring Objects--Types," defines objects, types, and the different type classes provided by VHDL.

- Section 4, "Constructs for Decomposing Design Functionality," identifies a number of VHDL constructs that allow the designer to decompose a complex design into smaller and more manageable modules.

- Section 5, "Global Considerations," describes some of the general issues you must consider when designing and modeling with VHDL.

- Section 6, "Coding Techniques," provides a number of hardware problems and some possible corresponding VHDL solutions.

- "Glossary," defines terms that appear in this manual and the *Mentor Graphics VHDL Reference Manual*.

### **Notational Conventions**

For information about VHDL syntax conventions used in this manual, refer to the *Mentor Graphics VHDL Reference Manual*. Also refer to the "BNF Syntax Description Method" section in the *Mentor Graphics VHDL Reference Manual*.

For information about general documentation conventions, refer to *Mentor Graphics Documentation Conventions*.

# **Related Publications**

In an effort to consolidate this information, the related publications list for VHDL can be found in the Related Publications section of the *Mentor Graphics VHDL Reference Manual*.

# Section 1 Overview

This section provides an overview of VHDL, which is based on IEEE Std 1076-1987, *IEEE Standard VHDL Language Reference Manual*. VHDL stands for VHSIC (Very High Speed Integrated Circuit) Hardware Description Language. The following list outlines the major topics covered in this section:

| General VHDL Modeling Principles | 1-3  |

|----------------------------------|------|

| Top-Down Design                  | 1-4  |

| Modularity                       | 1-4  |

| Abstraction                      |      |

| Information Hiding               | 1-9  |

| Uniformity                       |      |

| Summary                          | 1-11 |

VHDL is a design and modeling language specifically designed to describe (in machine- and human-readable form) the organization and function of digital hardware systems, circuit boards, and components.

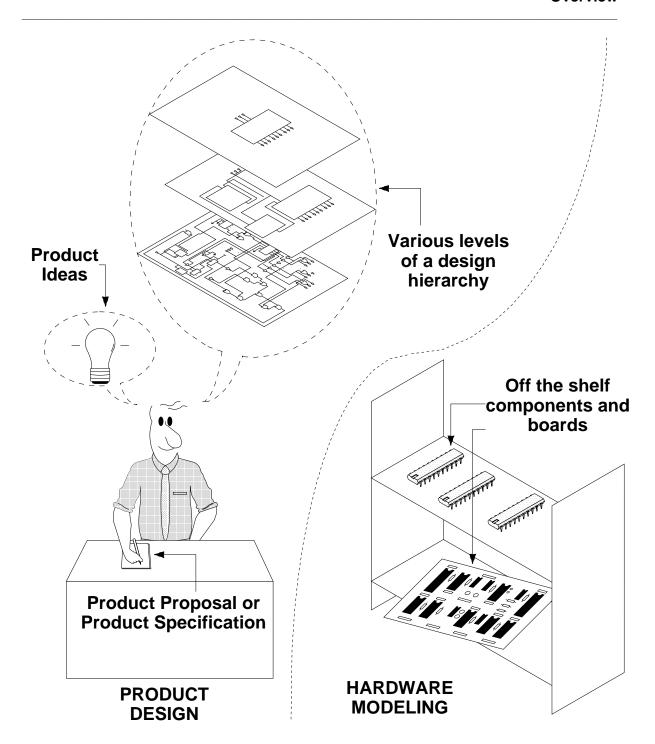

Figure 1-1 shows some of the various things that you can model with VHDL. This manual refers to a VHDL model as a textual description of a hardware design or piece of a design that, when simulated, mimics the design's behavior. A VHDL model can describe the behavior of either a new design or of pre-existing hardware. The terms VHDL description and VHDL model are used interchangeably. A design refers to the product under development whether it be a system, circuit board, or component.

Also refer to the discussion on "Designing or Modeling?" in the *Digital Modeling Guide*.

Figure 1-1. Various Things You Can Describe with VHDL

Designing refers to the process of developing new ideas into a product. Modeling usually refers to the process of creating a simulateable description (model) of the behavior of pre-existing products. (In Figure 1-1, this process is represented by the term Hardware Modeling.) Designing with VHDL involves creating and using models that you can simulate.

When you use VHDL as a design tool, you can describe a product idea, a product proposal (possibly the next step after the idea), a product specification, and then various design abstraction levels.

The compiled VHDL code provides a software model of your design or pre-existing hardware that you can test using digital simulators. In the hardware design process, you can analyze and refine your VHDL design description on a workstation before reaching the prototype stage.

VHDL descriptions that are created following VHDL synthesis guidelines can be run through a synthesis tool to create a gate-level implementation of the design.

# **General VHDL Modeling Principles**

Because VHDL is a powerful language, you can write hardware descriptions that satisfy two important goals:

- The VHDL descriptions will be easy to understand.

- The VHDL descriptions will be modifiable.

Easy-to-understand code benefits anyone who must read the code, especially if the original designer is not available to clarify any ambiguity.

Modifiable code is equally beneficial. There are several reasons why you might need to change your VHDL hardware description. For example, the hardware requirements may have changed as the design developed, or you may have found an error or timing problem during simulation of the software model.

In either case, VHDL supports the following principles that make it possible to write, modify, and maintain complex hardware design descriptions:

- Top-down design

- Abstraction

- Uniformity

- Modularity

- Information-hiding

The following subsections further describe these modeling principles and show how they help make complex hardware descriptions readable, easy to understand, and modifiable.

### **Top-Down Design**

When designing a complex hardware system or ASIC (application-specific integrated circuit), an engineer usually conceptualizes the design function with block diagrams at a high abstraction level. VHDL, within a Mentor Graphics simulation environment, allows you to

- Model the behavior of the high-level blocks

- Analyze (simulate) them

- Refine the high-level functionality as required before reaching the lower abstraction levels of design implementation

With the addition of the Mentor Graphics synthesis application, a VHDL design can be synthesized to the gate level.

Correcting design errors earlier in the design process is less costly than at the silicon or component implementation level.

### **Modularity**

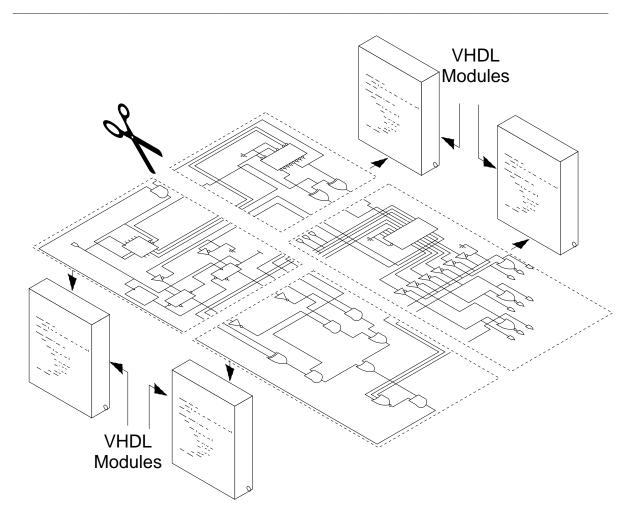

Modularity is the principle of partitioning (or decomposing) a hardware design and associated VHDL description into smaller units. Figure 1-2 shows a flat design (no hierarchy) partitioned into smaller units. When you design hardware with VHDL, the function of each hardware partition can be described with a module of code (represented as three-dimensional rectangular boxes in Figure 1-2). This makes the hardware description easier to manage and understand.

Figure 1-2. Flat-Level Partitioning of a Hardware Design

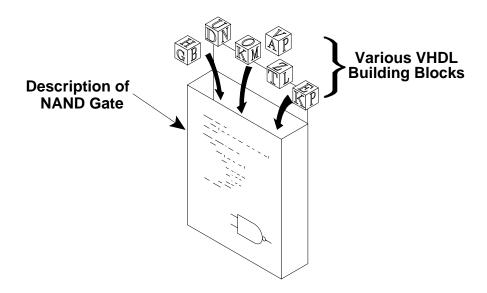

VHDL is composed of language building blocks that consist of over 75 reserved words and about 200 descriptive words or word combinations. Figure 1-3 illustrates how each VHDL module consists of various language building blocks. Figure 1-3 shows a module that represents a description of a NAND gate.

Figure 1-3. A Hardware Module Created from VHDL Building Blocks

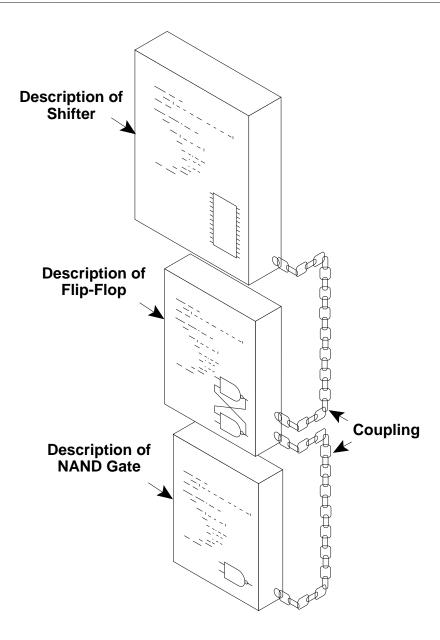

Figure 1-4 shows a hierarchical method of partitioning a design into smaller modules. The VHDL description of a shifter is partitioned into modules that describe the underlying structure. The shifter description contains an indirect reference to the NAND gate module. The structure of the shifter is described in a higher-level module as a series of interconnected flip-flops. In a lower-level module, the structure of the flip-flop is described as two interconnected NAND gates. In a separate module at an even deeper level, the function of a NAND gate is described. Each module is a self-contained description of the various parts used to describe a shifter.

The self-contained modules need to interface to other modules in a design in order to work as one unit. At the highest level, the shifter module in Figure 1-4 contains a well-defined interface that couples it to the flip-flop module. The flip-flop description at the middle level contains an interface that couples it to the lower-level description of the NAND gate.

Figure 1-4. Hierarchical Partioning of a VHDL Shifter Description

One reason to keep the description of the NAND gate and the flip-flop localized in separate modules is to make it possible to couple more than one high-level description to the lower-level modules. Localization makes the lower-level modules reusable and eliminates repetition. Another reason to localize the flip-flop and NAND gate modules is that the high-level description of the shifter is kept relatively simple and uncluttered.

It would not be a difficult task to modify the shifter description (such as adding more inputs and outputs) without changing the flip-flop or NAND gate descriptions. By using modularity in your VHDL descriptions, you meet the goals of keeping your description easy to understand and modifiable.

### **Abstraction**

An *abstraction* will group details (in a module) that describe the function of a design unit but does not describe how the design unit is implemented. This principle is closely related to modularity. In Figure 1-4, the flip-flop is an abstraction of the NAND gate level, and the shifter is an abstraction of the flip-flop level. Each abstraction is built from lower levels.

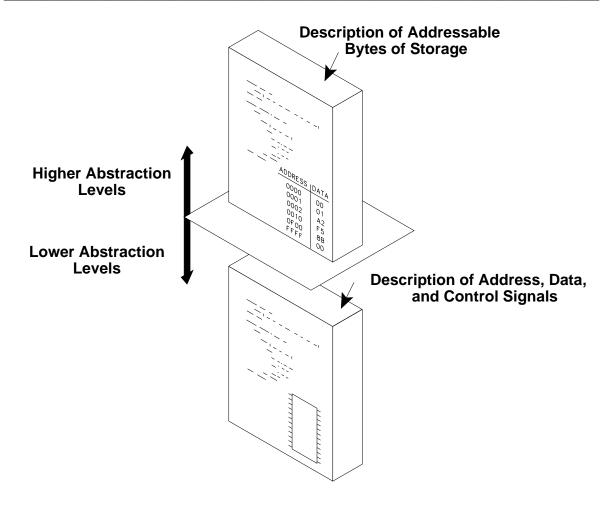

Figure 1-5 shows another way you can describe a hardware design using various levels of abstraction. A Read-Only-Memory (ROM) device is described at a high level as a series of address locations with corresponding data bytes stored in each location. At this level you do not care about address lines, data lines, or control lines. You can concentrate on the data byte assignments to selected addresses without thinking about the many signal lines that must be controlled at a lower level.

In the lower-level module, you can describe how each signal on the ROM pins must be configured to read or program each data storage location. If you needed to change the data stored in a given ROM location, you could go to the higher-level module and change a hex value associated with an address rather than redefine the states of many data lines. You again meet the modeling goals of keeping the design easy to understand and maintainable by using abstraction.

Figure 1-5. Applying Abstraction to a ROM Description

### **Information Hiding**

When coding a particular hardware module, it may be desirable to hide the implementation details from other modules. *Information hiding* is another useful principle for making VHDL designs manageable and easier to read. This principle complements abstraction, which extracts the functional details in a given module. By hiding implementation details from other modules, a designer's attention is focused on the relevant information while the irrelevant details are made inaccessible.

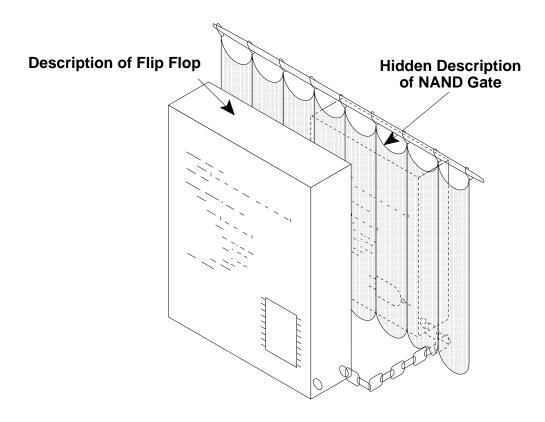

In the preceding VHDL shifter description (shown in Figure 1-4), the NAND gate level of abstraction can be hidden from the person who is coding the flip-flop description. Figure 1-6 shows a representation of this principle.

Figure 1-6. Hiding Unessential Details of NAND Gate Level

The person describing the flip-flop does not really care (at this level) how the NAND gate internals work. The NAND gate can be a previously-coded description that was compiled and stored in a library. The designer needs only to know how to interface to the input and output pins of the NAND gate. In this way, the flip-flop designer can ignore the details of how the NAND gate is implemented.

Another function of information hiding is to protect proprietary information when distributing VHDL models outside a company. By distributing only the compiled code (executable), the proprietary information (source code) can be hidden from its users.

### Uniformity

In addition to the principles of modularity, abstraction, and information-hiding, uniformity is another principle that helps to make your hardware description readable. *Uniformity* means that you create each module of code in a similar way by using the various VHDL building blocks. Uniformity implies good coding style, such as consistent code indentation and informative comments. For further information, refer to the "General VHDL Coding Guidelines" subsection on page 6-1.

# **Summary**

- VHDL is a modeling and design language specifically designed to describe (in machine- and human-readable form) the organization and function of digital hardware systems, circuit boards, and components.

- The following list describes several reasons why you would use VHDL to design and model your new product ideas or pre-existing hardware:

- O VHDL allows you to design, model, and test a system from the high level of abstraction down to the structural gate level.

- O VHDL descriptions created following by VHDL synthesis guidelines can be run through a synthesis tool to create gate-level implementations of designs.

- O Because this hardware language is based on IEEE Std 1076-1987, *IEEE Standard VHDL Language Reference Manual*, engineers throughout the design industry can use this language to minimize communication errors and incompatibility problems.

- O At Mentor Graphics, VHDL is integrated into one overall design environment. It is possible to do a system-level simulation mixing high-level, abstract descriptions with detailed gate-level models.

- VHDL supports the following principles that make it possible for you to write, modify, and maintain complex hardware design descriptions:

- O Top-down design--the method of describing (modeling) the behavior of the high-level blocks, analyzing (simulating) them, and refining the high-level

- functionality as required before reaching the lower abstraction levels of design implementation

- O Modularity--the principle of partitioning (or decomposing) a hardware design and the associated VHDL description into smaller units

- O Abstraction--grouping details (in a module) that describe the function of a design unit but do not describe how the design unit is implemented

- O Information-hiding-hiding the implementation details of one module from other modules

- O Uniformity--creating the design modules from the language building blocks in a consistent way

# Section 2 VHDL Fundamentals

This section introduces fundamental VHDL concepts and defines many of the terms associated with the language. Simple hardware examples are used throughout the section to illustrate many of the concepts. It is important to note that these examples may not represent ideal design or model solutions. In addition, they are not meant to provide you with a full understanding of each language building block but to give you a good introduction to the VHDL form.

Section 6 covers specific design tasks in further detail. The following list outlines the major topics covered in this section:

| VHDL Building Blocks                               | 2-2  |

|----------------------------------------------------|------|

| Major Language Constructs                          | 2-3  |

| Primary Language Abstraction                       | 2-5  |

| Design Description Methods                         | 2-10 |

| Structural Description                             | 2-10 |

| Behavioral Description                             | 2-14 |

| Data-Flow Description                              | 2-30 |

| Constructs Found in Each Design Description Method | 2-34 |

# **VHDL Building Blocks**

VHDL is composed of language building blocks that consist of more than 75 reserved words and about 200 descriptive words or word combinations. These building blocks are used to create the data types and instructions that make up a VHDL description.

*Reserved words* are words that have specific meaning to a VHDL compiler, such as the word **port**. Certain characters, such as the left and right parentheses and the semicolon, are also classified as reserved words. Do not use reserved words except as defined by VHDL.

Examples of descriptive word combinations are "port clause" and "port list". Although these word combinations would not appear in actual code, they provide a name to the building blocks that you use when building a VHDL description.

The building blocks of VHDL are called *language constructs*. A language construct is an item that is constructed from basic items such as reserved words or other language building blocks. For example, the syntax diagram in Figure 2-1 shows that the language construct called port\_clause is composed of the following: the reserved word **port** followed by the reserved word "(", another building block called a port\_list, the reserved word ")", and finally the reserved word ";". Those items enclosed in an oval or circle appear verbatim in the VHDL code. Items enclosed in rectangles are other language constructs that are defined in separate syntax diagrams.

Figure 2-1. Port Clause Syntax Diagram

For a complete listing of VHDL reserved words and syntax diagrams for each language construct, refer to the *Mentor Graphics VHDL Reference Manual*.

This manual presents syntax information in a summary format that suggests how the real code looks. The right column of the following syntax example shows the syntax summary for port clause:

port clause ..... port ( port\_list ) ;

Examples presented in this format do not always show which items in the syntax are optional or which ones you can use more than once. For the detailed information, you should consult the syntax diagrams and the BNF diagrams in the *Mentor Graphics VHDL Reference Manual*.

# **Major Language Constructs**

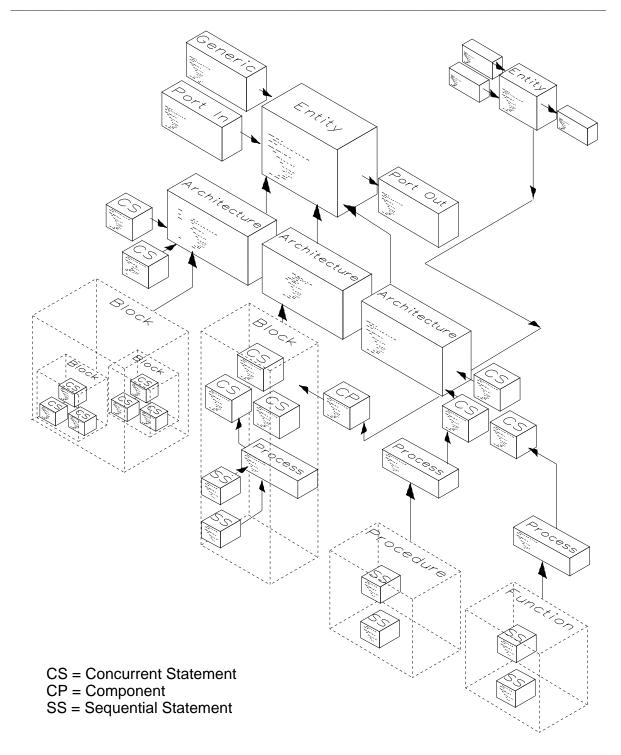

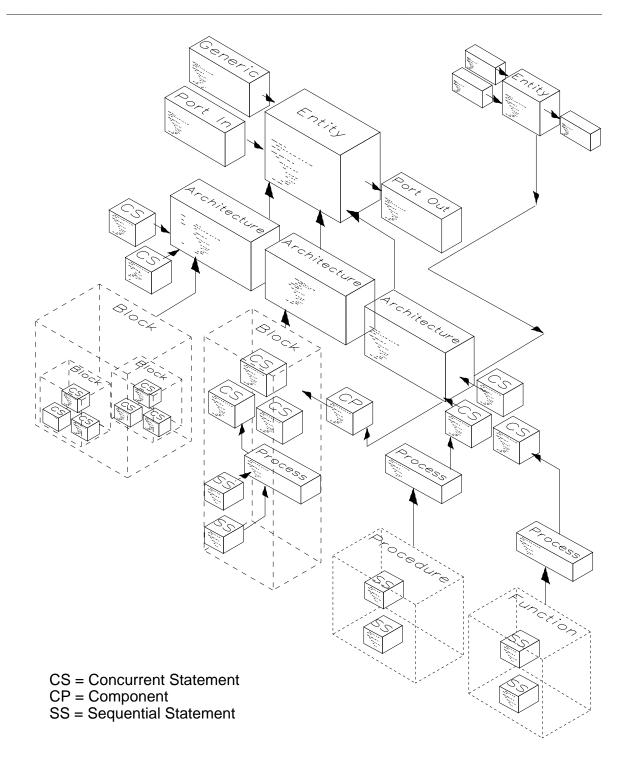

Figure 2-2 shows the hierarchy of the major language constructs. Each block in the figure represents a major language construct and shows its position relative to other constructs. The following paragraphs briefly introduce some of the constructs that are further explained in later subsections. You might want to refer to Figure 2-2 when reading about the various language constructs in the later subsections.

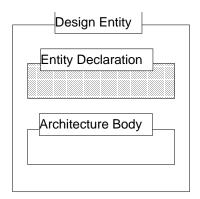

At the top of the pyramid-like structure in Figure 2-2 is the *design entity*. A design entity is the basic unit of a hardware description.

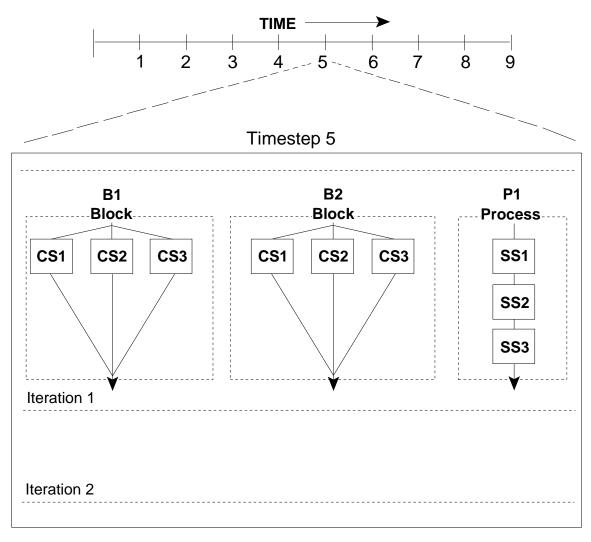

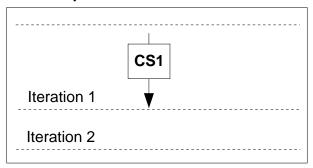

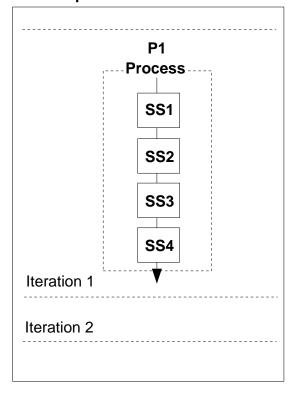

At the next level, the figure shows that a design entity is composed of one or more architectures. The architecture describes the relationships between the design entity inputs and outputs. Each architecture consists of concurrent statements, denoted as CS in Figure 2-2. Concurrent statements define interconnected processes and blocks that together describe a design's overall behavior or structure.

You can group concurrent statements using the block statement. This grouping is represented by a dashed block in Figure 2-2. Groups of blocks can also be partitioned into other blocks. At this same level, a VHDL component (denoted as CP in Figure 2-2) can be instantiated and connected to defined signals within the blocks. The VHDL component is a reference to an entity.

Figure 2-2. Major Language Construct Hierarchy

A process can be a single signal assignment statement or a series of sequential statements (denoted as SS in Figure 2-2). Within a process, block, or package, procedures and functions can partition the sequential statements. Refer to the "Locating Language Constructs" appendix in the *Mentor Graphics VHDL Reference Manual* for information on where major constructs can be positioned within a VHDL design description.

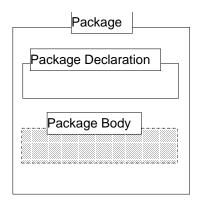

A package (not shown in the figure) allows you to group a collection of related items for use by one or more separate modules of code.

# **Primary Language Abstraction**

During the design process you usually decompose hardware designs into smaller, more manageable units. VHDL supports this hardware decomposition and makes it possible for you to write a hardware description so that many of the smaller parts are reusable by different portions of the overall design (or even other designs).

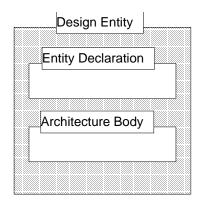

The primary abstraction level of a VHDL hardware model is the design entity. The design entity can represent a cell, chip, board, or subsystem.

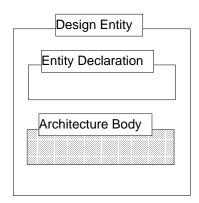

A design entity is composed of two main parts: an entity declaration and an architecture body\*.

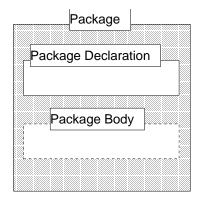

Entity declarations and architecture bodies are two of the VHDL language library units. A library unit is a portion of the hardware description (model) that can be contained and compiled in a separate design file. (Package declarations and package bodies are two other library units.) This capability allows you to modularize a design description by compiling each entity or package declaration separate from the corresponding body.

<sup>\*</sup>Refer to the appropriate syntax diagrams in the *Mentor Graphics VHDL Reference Manual* for a listing of all the possible building blocks in an entity declaration and an architecture body.

An entity declaration defines the interface between the design entity and the environment outside of the design entity. The structure of an entity declaration is shown in the following example:

```

entity identifier is

entity_header

-- (generic and/or port clauses)

entity_declarative_part

-- (declarations for subprograms,

-- types, signals, ...)

begin

entity_statement_part

end identifier;

```

The entity identifier is a descriptive name that you assign. Each design entity receives information from the outside via a port (of mode **in**) or a generic interface. The design entity sends out information via a port (of mode **out**). Also see the top of Figure 2-2 on page 2-4.

A generic interface defines parameters (such as delay data) that can be passed into the entity when it is instantiated\*. Generics allows you to define a reusable design entity with variable parameters that can be customized for each use of the design entity.

The basic format of a generic clause and a port clause are shown as follows:

```

generic clause ...... generic ( generic_list );

port clause ...... port ( port_list );

```

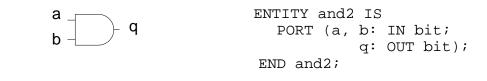

The following example shows an entity declaration (including a port clause) for the simple two-input AND gate shown at the left. The convention used in this manual to identify reserved words within code examples is to display them in all uppercase characters. Also refer to the Notational Conventions section in the *Mentor Graphics VHDL Reference Manual*.

<sup>\*</sup>Passing parameters in this way is further explained in the "Component Instantiation" subsection on page 4-7.

The architecture body describes the relationships between the design entity inputs and outputs. The structure of this construct is shown in the following example:

architecture identifier of entity\_name is

architecture\_declarative\_part

begin

architecture\_statement\_part

end identifier;

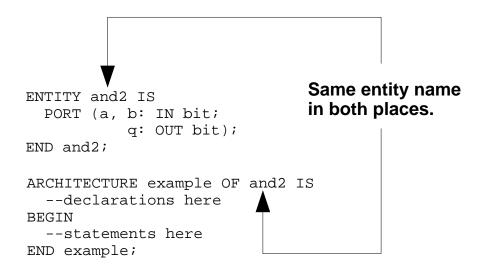

The identifier and entity\_name are words that you provide in your VHDL code. The entity name in the architecture body must be the same as the identifier of the corresponding entity declaration as shown in Figure 2-3.

Figure 2-3. Entity Name Usage in Entity Declaration and Architecture Body

You define the behavior or structure of a design entity in the architecture body using one or more methods described in the "Design Description Methods" subsection, beginning on page 2-10.

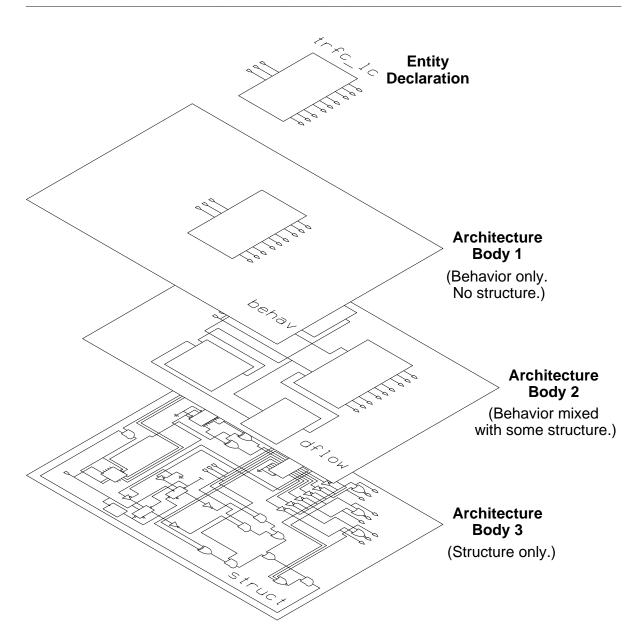

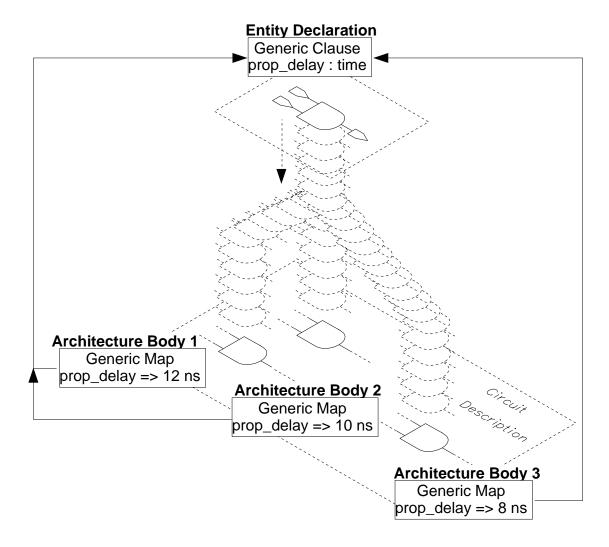

A given design entity may have more than one architecture body to describe its behavior and/or structure as shown in Figure 2-4.

You would write the entity declaration (entity name could be "trfc\_lc" as indicated at the top of Figure 2-4) and compile it. Then you could write and compile a high-abstraction level behavioral description of the circuit. The architecture name could be "behav" as shown in the lower-right corner of Architecture Body 1 in Figure 2-4.

Once you are satisfied that the circuit behavior (at the high-abstraction level) is functioning, you can write another architecture body to test circuit functions at a lower-abstraction level. Architecture Body 2 in Figure 2-4 includes some structure and data flow details. The architecture name of this body is "dflow."

Then you can simulate this second level architecture and make refinements to Architecture Body 2 as required until the expected results are achieved.

The lowest abstraction level you write could be a structural description of the circuit that implements the design function at the component level. Architecture Body 3 in Figure 2-4 represents this abstraction level. The architecture name of this body is "struct."

Using three different architecture bodies for this one design allows you to develop the circuit description using top-down methodology. Each abstraction level is documented and saved in a separate design file.

Figure 2-4. Multiple Architecture Bodies for One Entity Declaration

# **Design Description Methods**

VHDL provides a textual method of describing a hardware design in place of a schematic representation. The following list shows the various VHDL methods for describing hardware architectures:

- *Structural description* method expresses the design as an arrangement of interconnected components.

- Behavioral description method describes the functional behavior of a

hardware design in terms of circuits and signal responses to various stimuli.

The hardware behavior is described algorithmically without showing how it is

structurally implemented.

- Data-flow description method is similar to a register-transfer language. This method describes the function of a design by defining the flow of information from one input or register to another register or output.

All three methods of describing the hardware architecture can be intermixed in a single design description.

### **Structural Description**

This subsection uses a two-input multiplexer to identify some of the language constructs in a VHDL structural description. This description provides an overview and not a complete representation of all the language building blocks found in a structural description. Refer to the appropriate syntax diagrams in the *Mentor Graphics VHDL Reference Manual* for a complete flow of the language constructs described in this subsection.

A VHDL structural description of a hardware design is similar to a schematic representation because the interconnectivity of the components is shown. This similarity is illustrated in this subsection with a comparison of a simple schematic design to a VHDL structural description of the same circuit.

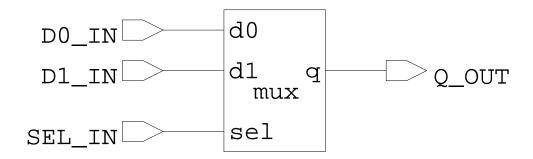

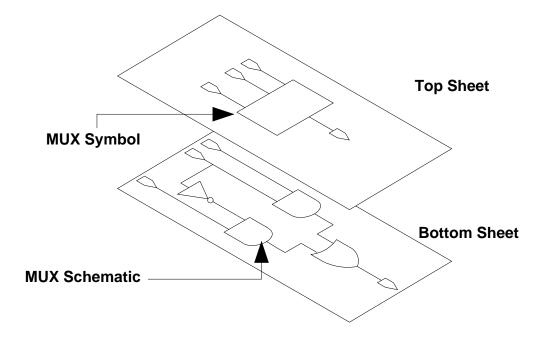

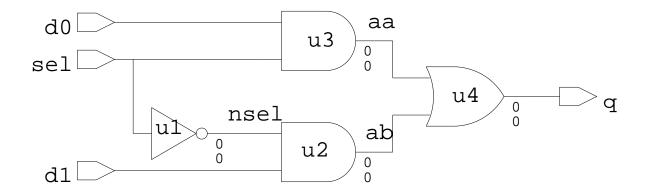

Figure 2-5 shows the symbol of a two-input multiplexer (MUX). This MUX is a hierarchical design, as shown in Figure 2-6, with the bottom sheet containing the schematic representation or description of the internal structure, as shown in Figure 2-7. Note the pin names on the inside of the MUX symbol in Figure 2-5 match the net names of the inputs and output of the schematic in Figure 2-7.

Figure 2-5. Symbol Representation of Two-Input Multiplexer

Figure 2-6. A Schematic Editor Hierarchical Design of a Multiplexer

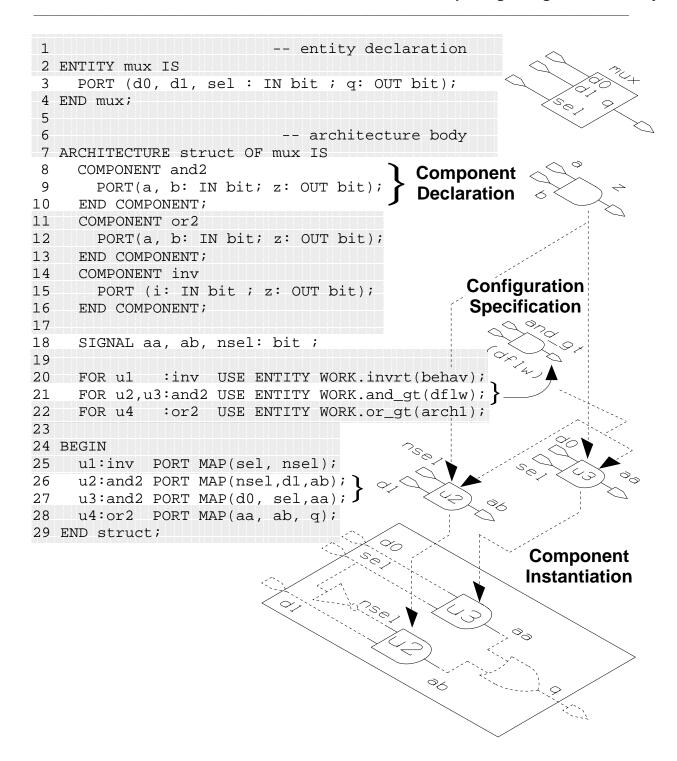

Figure 2-8 shows a VHDL structural description of the two-input multiplexer. The VHDL code contains comments that are set off with a double dash (--). Any text appearing between the double dash and the end of a line is ignored by the compiler. (See lines 1,2, 5, 7, 17, 19 through 21, and 24 in Figure 2-8.) Descriptive comments make the code easier to read.

Figure 2-7. Gate-Level Representation of Two-Input Multiplexer

```

ENTITY mux IS

-- entity declaration

1

2

PORT (d0, d1, sel: IN bit; q: OUT bit); --port clause

3

END mux;

4

5

-- architecture body

ARCHITECTURE struct OF mux IS

6

7

COMPONENT and 2

--architecture decl. part

8

PORT(a, b: IN bit; c: OUT bit);

9

END COMPONENT;

10

COMPONENT or 2

PORT(a, b: IN bit; c: OUT bit);

11

12

END COMPONENT;

13

COMPONENT inv

14

PORT (a: IN bit; c: OUT bit);

15

END COMPONENT;

16

17

SIGNAL aa, ab, nsel: bit;

--signal declaration

18

19

FOR u1

:inv USE ENTITY WORK.invrt(behav); -- config.

20

FOR u2, u3:and2 USE ENTITY WORK.and_gt(dflw); -- specif.

FOR u4 :or2 USE ENTITY WORK.or_gt(arch1); --

21

22

23

BEGIN

24

ul:inv PORT MAP(sel, nsel); -- architecture statement part

u2:and2 PORT MAP(nsel,d1,ab);

25

26

u3:and2 PORT MAP(d0, sel,aa);

27

u4:or2 PORT MAP(aa, ab, q);

28

END struct;

```

Figure 2-8. Code of Structural Description for a Multiplexer

The two-input MUX represented by Figure 2-8 is a basic design unit. The entity declaration at the top of Figure 2-8 (lines 1 through 3) defines the interface between the design entity and the environment outside of the design entity.

This entity declaration contains a port clause that provides input channels (signals a0, a1, and sel in Figure 2-8, line 2) and an output channel (signal q in Figure 2-8, line 2). The signals are of a predefined type called bit which is declared elsewhere to describe all possible values (0 or 1) for each signal. (Types are described on page 3-1.) This entity declaration can be compared with the MUX symbol in the schematic design in Figure 2-6.

The architecture body in Figure 2-8 (lines 6 through 28) describes the relationships between the design entity inputs and outputs structurally. This architecture body performs a function similar to the bottom sheet in the schematic design in Figure 2-6.

The various components (and2, or2, and inv) that form the mux design entity in Figure 2-8 are declared in the architecture declarative part (lines 7 through 15). Signals (aa, ab, and nsel) are also declared in the architecture body (line 17) to represent the output of the two AND gates (u2 and u3) and the inverter (u1).

The configuration specifications in lines 19 through 21 bind each component instance to a specific design entity which describes how each component operates. For example, the component u1 used in line 24 of Figure 2-8 is bound to an architecture body called behav for a design entity called invrt.

The architecture statement part (lines 24 through 27) describes the connections between the components within the design entity. In this part, the declared components are instantiated. (For more information on component declaration and instantiation, see "Component Instantiation" on page 4-7.)

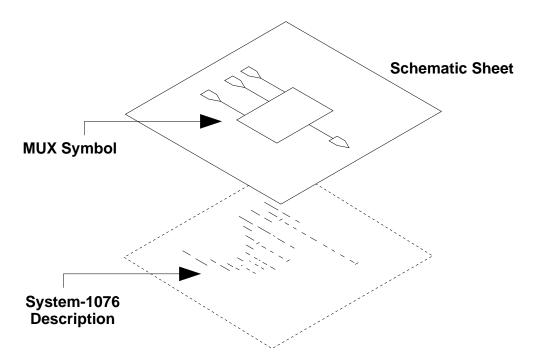

Figure 2-9 shows how a schematic sheet could contain a MUX symbol with an associated VHDL structural description. Instead of using an underlying schematic sheet, the VHDL structural description defines the internal structure of the component.

In the design shown in Figures 2-6 through 2-9, the behavior of the MUX was determined by the connections between the inverter, the AND gates, and the OR gate. The function of these gates is generally understood.

In a more complex design, the components u1 through u4 in Figure 2-8 could represent entities that have complicated functions such as a central processing unit or a bus controller. When function and not structure is most important, you can describe each component with a corresponding behavioral description.

Figure 2-9. Two-Input Multiplexer with Associated Structural Description

#### **Behavioral Description**

A VHDL behavioral description represents the function of a design in terms of circuit and signal response to various stimulus. This subsection identifies some of the major language constructs found in a behavioral description using the previous MUX example and a four-bit shifter example. Refer to the appropriate syntax diagrams in the *Mentor Graphics VHDL Reference Manual* for a complete flow of the language constructs described in this subsection. After reading the previous subsection on structural descriptions, you can compare that method with the behavioral description method that is described in this subsection.

Figure 2-10 shows a behavioral description of the mux example described in the structural description subsection. Like the structure description, you can include the MUX symbol on a schematic sheet, except this time, the VHDL model defines the behavior, of the component during circuit simulation.

The behavioral description in Figure 2-10 and the structural description in Figure 2-8 both contain an entity declaration and an architecture body. In practice, you most likely would not have both the behavioral and structural architecture body shown in Figures 2-8 and 2-10 in one source file (although it is possible). You can first write the entity declaration in one design file, then the behavioral architecture in another design file, and the structural architecture in still another design file.

In an actual design, after the entity declaration is written and compiled, you might next write a behavioral architecture to allow testing of the overall circuit functions. After you simulate and refine the functional model, you then might write a structural architecture. You can substitute the structural architecture body for the behavioral and then the model can be simulated again.

```

1

ENTITY mux IS

-- entity declaration

2

PORT (d0, d1, sel: IN bit; q: OUT bit); --port clause

3

END mux;

-- architecture body

5

ARCHITECTURE behav OF mux IS

6

BEGIN

7

f1:

-- process statement

PROCESS (d0, d1, sel) -- sensitivity list

8

9

BEGIN

IF sel = '0' THEN -- process statement part

10

11

q \ll d1;

12

ELSE

13

q \le d0;

14

END IF;

15

END PROCESS f1;

16

END behav;

```

Figure 2-10. Code of Behavioral Description for a Multiplexer

A behavioral description model is also useful to stimulate inputs of other VHDL models during simulation. For example, you might have designed a traffic light controller using a structural description and now you wish to test it. The traffic

light controller has inputs that connect to traffic sensors. For simulation purposes, you could include a behavioral model that stimulates the sensor inputs in a predefined test pattern.

The major difference between the structural and behavioral descriptions of the MUX is that the architecture body in Figure 2-10 contains a process statement. The process statement describes a single, independent process that defines the behavior of a hardware design or design portion. The basic format of a process statement is shown as follows:

The process statement in Figure 2-10 begins with the process label £1 followed by a colon (line 7). The process label is optional but is useful to help differentiate this process from other processes in a larger design.

Following the reserved word **process** is an optional sensitivity list (located between the parentheses). The sensitivity list in Figure 2-10 (line 8) consists of the signal names d0, d1, and sel. During simulation, whenever a signal in the sensitivity list changes state, the statements in that process are executed. In the MUX example, whenever d0, d1, or sel changes state, process f1 is executed and the state of the output signal is changed accordingly. Each process in a VHDL design description is executed once during initialization of the VHDL model.

The heart of the process statement in Figure 2-10 is the 'if' statement that is contained in the process statement part. The basic format of an if statement is shown as follows:

if statement ..... if condition then

sequence\_of\_statements

elsif condition then

sequence\_of\_statements

else

sequence\_of\_statements

sequence\_of\_statements

end if;

The VHDL if statement is interpreted similarly to an English sentence. For example, look at the following sentence:

If the traffic light is green, then proceed across the intersection or else (if the traffic light is not green) remain stopped.

The sentence has a condition that must be satisfied (If the traffic light is green) before the command (proceed across the intersection) is executed. The "else" part of the sentence gives the alternative command (or else remain stopped) if the condition is not satisfied.

The if statement in Figure 2-10 (lines 10 through 14) can be rewritten as the following sentence:

If signal sel (select) is equal to 0, then assign the value of the waveform on signal dl to target signal q or else assign the value of the waveform on signal dl to target signal q.

Once the if condition or the else condition in this example is satisfied (sel = '0' or its opposite where sel does not equal '0'), target signal q is modified according to the appropriate signal assignment statement. The basic format of a signal assignment statement is as follows:

signal assignment statement: target <= **transport** waveform; (Note that **transport** is optional.)

The following is the first signal assignment statement in Figure 2-10:

This statement assigns the waveform on signal d1 to target signal q. The optional reserved word **transport**\* is not used in this example. The signal assignment delimiter consists of the two adjacent special characters <=, also called a compound delimiter. The following is the second signal assignment statement in this example. This statement assigns the waveform of signal d0 to the target signal q:

13

$$q \le d0;$$

Another use of the compound delimiter <= is as the relational operator "less than or equal to" in conditions such as the following:

IF

$$z \le '1'$$

THEN

The other relational operators are shown in Table 5-1 on page 5-11.

In summary, the signal assignment delimiter <= is used to assign the value on the right side of the delimiter to the target on the left side. The same compound delimiter <= is used as the relational operator "less than or equal to" in test conditions such as the if statement. How this delimiter is used in context determines whether it is a signal assignment delimiter or a relational operator.

Figure 2-11 shows a VHDL behavioral description of a four-bit shifter. To see how accurate and succinct the VHDL description is, compare it with the following textual description:

The four-bit shifter has four input data lines, four output data lines, and two control lines. When both control lines are low, the input levels are passed directly to the corresponding output. When control line 0 is high and control line 1 is low, output line 0 is low; input line 0 is passed to output line 1; input line 1 is passed to output line 2; and input line 2 is passed to output line 3. When control line 0 is low and control line 1 is high, input line 1 is passed to output line 0; input line 2 is passed to output line 1; input line 3 is passed to output line 2; and output line 3 is low. When both control lines are high, input line 0 is passed to both output line 0 and line 1; input line 1 is passed to output line 2; and input line 2 is passed to output line 3.

<sup>\*</sup>Refer to the Glossary entry for the reserved word **transport** for further information.

```

1

ENTITY shifter IS

-- entity declaration

PORT ( shftin : IN bit_vector(0 TO 3); --port clause

2

3

shftout : OUT bit_vector(0 TO 3);

shftctl : IN bit_vector(0 TO 1) );

4

5

END shifter;

6

ARCHITECTURE behav OF shifter IS -- architecture body

7

8

BEGIN

9

f2:

-- process statement

10

PROCESS (shftin, shftctl)

VARIABLE shifted : bit_vector(0 TO 3); -- proc. decl. part

11

12

13

CASE shftctl IS

--proc. stmnt part

14

WHEN "00" => shifted := shftin;

WHEN "01" => shifted := shftin(1 TO 3) & '0';

15

WHEN "10" => shifted := '0' & shftin(0 TO 2);

16

WHEN "11" => shifted := shftin(0) & shftin(0 TO 2);

17

18

END CASE;

19

shftout <= shifted AFTER 10 ns;</pre>

20

END PROCESS f2;

21

END behav;

```

Figure 2-11. Code Example of Behavioral Description for a Shifter

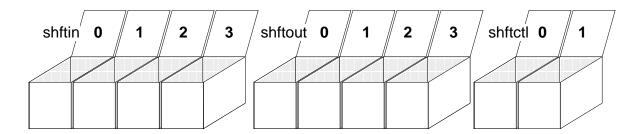

The port clause in Figure 2-11 (lines 2 through 4) identifies the input ports as shftin (shifter data in) and shftctl (shifter control) and the output port as shftout (shifter data out). This port clause defines the input and output ports as an array of bits using the predefined type bit\_vector. Types are described on page 3-1.

The arrays can be compared with containers that have labeled compartments for data storage as shown in Figure 2-12. For example, the array named shftin has four elements referred to as shftin(0), shftin(1), shftin(2), and shftin(3). Each element is a storage area for data; in this case, they are storage areas for bit information.

Figure 2-12. Arrays Represented as Data-Storage Containers

The architecture body in Figure 2-11 contains a process statement (lines 9 through 20) as does the previous MUX behavioral example. One difference between the two examples is that the process statement in the shifter example contains a process declarative part (line 11) composed of a variable declaration. A variable declaration has the following format:

```

variable declaration .......

variable identifier_list :

subtype_indication := expression ;

```

The variable declaration in Figure 2-11 does not include the optional ":= expression" part. The variable shifted holds the shifted value of the shftin bit vector. It is important that shftin and shifted are of the same type, in this case, an array of bits with four elements.

The variable declaration states that shifted is an array of bits from 0 to 3. The bit vector shifted appears later (after the case statement) in the signal assignment:

```

19 shftout <= shifted AFTER 10 ns;

```

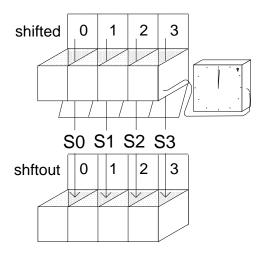

This signal assignment statement includes the reserved word **after** to specify the propagation time expected for the shftin array of waveforms (stored in the variable array shifted) to reach the shftout array of target signals. Figure 2-13 shows how the elements in array shifted map one-for-one to the elements in array shftout. The 10 ns delay is represented by a timer that determines the time when the waveforms are transferred. Labels S0 through S3 represent the values that were stored in shftin and then passed to the variable shifted.

Figure 2-13. Variable Assignment for SHFTOUT Array After 10 ns

The previous MUX behavioral example uses an if statement to assign a waveform to a target signal when a given condition is satisfied. The shifter example uses a case statement to perform a similar function. A case statement executes one out of a number of possible sequences of statements as determined by the value of an associated expression. The basic format of a case statement is shown as follows:

case statement ......

when choices => --case stmnt alternative

sequence\_of\_statements

end case;

The case statement in Figure 2-11 (lines 13 through 18 in the process statement part) contains four case statement alternatives for the shftctl array, shftctl(0) and shftctl(1). When one of the alternatives is true, the associated variable assignment statement is executed. A variable assignment statement replaces the current variable value (target) with a new value as specified by an expression. A variable assignment statement has the following format:

variable assignment stmnt target := expression

The characters := are used together as the variable assignment delimiter. To better understand the variable assignment process, consider each of the case statement alternatives from Figure 2-11 one at a time starting with the following:

```

14 WHEN "00" => shifted := shftin;

```

According to this case statement alternative, when shftctl(0) equals 0 and shftctl(1) equals 0, then the variable array shifted is assigned the values in the array shftin. The compound delimiter '=>' separates the choices (WHEN "00") from the sequence of statements (shifted := shftin;).

The alignment of data in an array is determined by the order in which the array is declared. The port clause defines array shftctl as follows:

```

4 shftctl : IN bit_vector(0 TO 1)

```

The order of data in the array shftctl is 0 to 1 (ascending). Any reference to shftctl follows this ordering. Therefore, the first 0 (from the left) in the phrase WHEN "00" refers to the state of shftctl(0) and the second 0 (from the left) refers to the state of shftctl(1).

The order of data in the arrays shftin and shftout is defined in the port clause as 0 to 3 (ascending order). The variable shifted is defined in the process declarative part as 0 to 3 (ascending).

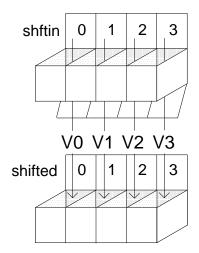

Figure 2-14 shows how the elements in array shftin map one-for-one to the elements in array shifted during execution of the following case statement alternative:

```

14 WHEN "00" => shifted := shftin;

```

Labels V0 through V3 represent the values that are passed from each shftin array element.

Figure 2-14. Variable Assignment for Array When SHFTCTL = 00

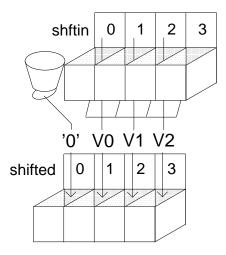

Figure 2-15 shows how the elements in array shftin map to the elements in array shifted during execution of the following case statement alternative:

15 WHEN "01" => shifted := shftin(1 TO 3) & '0';

Figure 2-15. Variable Assignment for Array When SHFTCTL = 01

Note that only three elements (1, 2, and 3) of the shftin array are transferred to the shifted array. The fourth value ('0') is concatenated to the arrayshftin by using the concatenation operator &. The '0' is transferred along with the other shftin values. For a complete description of the concatenation operator, see the

"Adding Operators" section in the Mentor Graphics VHDL Reference Manual.

Figure 2-16 shows how the elements in array shftin map to the elements in array shifted during execution of the following case statement alternative:

```

16 WHEN "10" => shifted := '0' & shftin(0 TO 2);

```

In this alternative, the value '0' is assigned to the first element of arrayshifted (shifted(0)) and the values of shftin(0 to 2) are concatenated to the '0' and assigned to array elements shifted(1) through shifted(3).

Figure 2-16. Variable Assignment for Array When SHFTCTL = 10

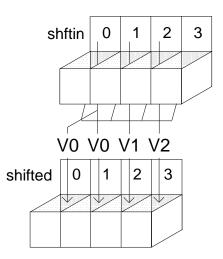

Figure 2-17 shows how the elements in array shftin map to the elements in array shifted during execution of the following case statement alternative:

```

17 WHEN "11" => shifted := shftin(0) & shftin(0 to 2);

```

The value of shftin(0) is assigned to two elements of array shifted (shifted(0) and shifted(1)).

Figure 2-17. Variable Assignment for Array When SHFTCTL = 11

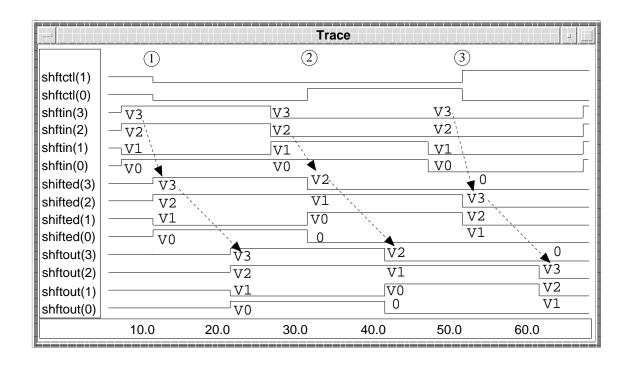

To show further what happens when process £2 is executed in the VHDL shifter example, three conditions of the shftctl array are represented in the waveform drawing of Figure 2-18 as follows:

```

1. WHEN "00" => shifted := shftin;

2. WHEN "10" => shifted := '0' & shftin(0 to 2);

3. WHEN "01" => shifted := shftin(1 to 3) & '0';

```

Each number at the top of the waveform drawing relates to the corresponding condition in the previous numbered list. Arbitrary waveforms (data values) have been assigned to the shftin array elements shftin(3) to shftin(0). The values of the shftin array elements are labeled V3 to V0 for each condition represented. The arrows show how the values flow from the shftin array to the shifted array (when the shftctl signals change state) and then to the shftout array 10 ns later.

1. Because shftctl(1) and shftctl(0) are both low in condition 1, the values on shftin(3) to shftin(0) (V3 to V0) pass to the corresponding shifted array elements. Ten nanoseconds later, the same values pass from the shifted array elements to the shftout array elements as determined by the conditional signal assignment:

```

19 shftout <= shifted AFTER 10 ns;

```

A conditional signal assignment is further described on page 2-31.

- 2. Because shftctl(1) is high and shftctl(0) remains low in condition 2, the following conditions occur: a low (0) is forced on shifted(0), shifted(1) takes on the high value from shftin(0), shifted(2) remains high because of the high value from shftin(1), and shifted(3) takes on the low value from shftin(2).

- 3. Because shftctl(1) is low and shftctl(0) is high in condition 3, the following conditions occur: a low (0) is forced on shifted(3) so it remains low, shifted(0) takes on the low value from shftin(1) so it remains low, shifted(1) takes on the low value from shftin(2), and shifted(2) takes on the low value from shftin(3).

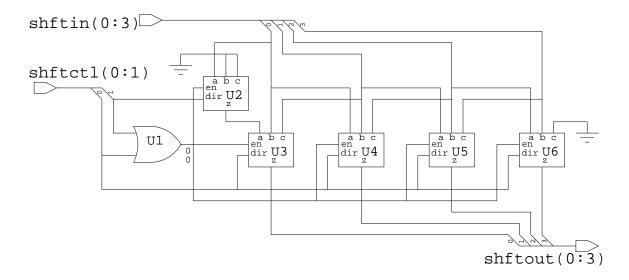

To provide a complete picture of the four-bit shifter example, the structure is shown in the schematic of Figure 2-19.

Figure 2-18. Four-Bit Shifter Waveforms

Figure 2-19. Schematic for a Four-Bit Shifter

#### Structural and Behavioral Description Summary

To summarize the preceding structural and behavioral description methods:

A VHDL structural description defines the interconnectivity of various components. A behavioral description algorithmically defines circuit and signal response to various stimuli.

A design entity is the basic unit of a hardware description that represents a cell, chip, board, or subsystem. Both the structural and behavioral descriptions declare each design entity with an entity declaration. An associated architecture body describes the relationships between the design entity inputs and outputs.

The structural and behavioral descriptions largely differ in the architecture body, as shown in the comparison of the MUX examples in Figure 2-20. The architecture body of the structural description, as shown in the top part of Figure 2-20, contains an architecture statement part that describes the interconnectivity of the components within the design entity. The architecture body of the behavioral description, shown in the bottom part of Figure 2-20, contains a process statement that describes the behavior of the declared design entity.

If a model contains a signal assignment statement or a concurrent statement that has an associated signal assignment statement, it is *not* a structural description. If a model contains a component instantiation statement, it is *not* a behavioral description.

```

ENTITY mux IS -- STRUCTURAL ----- entity declaration

1

2

PORT (d0, d1, sel: IN bit; q: OUT bit); --port clause

3

END mux;

5

ARCHITECTURE struct OF mux IS -- architecture body

COMPONENT and2

--architecture decl. part

7

PORT(a, b: IN bit; c: OUT bit);

END COMPONENT, COMPONENT or 2

8

END COMPONENT;

9

10

PORT(a, b: IN bit; c OUT bit);

11

END COMPONENT;

12

COMPONENT inv

13

PORT (a: IN bit; c: OUT bit);

14

END COMPONENT;

15

SIGNAL aa, ab, nsel: bit; --signal declaration

16

17

FOR ul :inv USE ENTITY WORK.invrt(behav); -- config.

18

FOR u2, u3:and2 USE ENTITY WORK.and_gt(dflw); -- specif.

19

FOR u4 :or2 USE ENTITY WORK.or_gt(arch1); --

20

21 BEGIN

ul:inv PORT MAP(sel, nsel); --architecture statement part

22

23

u2:and2 PORT MAP(nsel,d1,ab);

24

u3:and2 PORT MAP(d0, sel,aa);

25

u4:or2 PORT MAP(aa, ab, q);

26

END struct;

ENTITY mux IS ----BEHAVIORAL---- entity declaration

PORT (d0, d1, sel: IN bit; q: OUT bit); --port clause

2

3

END mux;

-- architecture body

ARCHITECTURE behav OF mux IS

6

BEGIN

7

f1:

-- process statement

PROCESS (d0, d1, sel) -- sensitivity list

8

BEGIN

9

IF sel = '0' THEN

10

-- process statement part

11

q \ll d1;

12

ELSE

13

q \ll d0;

Q <=

END IF;

14

15

END PROCESS f1;

16

END behav;

```

Figure 2-20. Comparing Structural and Behavioral Descriptions

#### **Data-Flow Description**

The following identifies some of the major language constructs found in a data-flow description using the previous MUX and four-bit shifter examples.

A VHDL data-flow description and a register-transfer language description are similar in that they describe the function of a design by defining the flow of information from one input or register to another register or output.

The data-flow and behavioral descriptions are similar in that both use a process to describe the functionality of a circuit. A behavioral description uses a small number of processes where each process performs a number of sequential signal assignments to multiple signals. In contrast, a data-flow description uses a large number of concurrent signal assignment statements. Concurrent statements used in data-flow descriptions include the following:

- Block statement (used to group one or more concurrent statements)

- Concurrent procedure call

- Concurrent assertion statement

- Concurrent signal assignment statement

In addition to these language constructs, the process statement, generate statement, and component instantiation statement are also concurrent statements. These three additional concurrent statements are not usually found in a data-flow description.

Concurrent statements define interconnected processes and blocks that together describe a design's overall behavior or structure. A concurrent statement executes asynchronously with respect to other concurrent statements. The subsection "Contrasting Concurrent and Sequential Modeling" on page 4-28 provides more information on how concurrent statements execute.

Figure 2-21 can be considered a data-flow description of the same MUX example used in the previous behavioral and structural description examples. This example is too simple to show the usefulness of a data-flow description because it is almost identical to the behavioral description in Figure 2-10 on page 2-15.

Both examples use one process statement (implied with the concurrent signal assignment statement in Figure 2-21, lines 8 through 10) to define signal behavior.

```

-- entity declaration

1

ENTITY mux IS

PORT (d0, d1, sel: IN bit; q: OUT bit); -- port clause

2

3

END mux;

4

5

-- architecture body

ARCHITECTURE data flow OF mux IS

6

7

BEGIN

8

--concurrent sig. assgnmnt stmnt

cs1 :

q <= d1 WHEN sel = '0' ELSE --conditional sig. assqnmnt

9

10

d0 ;

END data flow;

11

```

Figure 2-21. Example of Data-Flow Description for a Multiplexer

The data-flow description contains the same entity declaration (lines 1 through 3) used in the previous structural and behavioral description examples. The architecture body contains a concurrent signal assignment statement that represents an equivalent process statement that has the same meaning. The format of a concurrent signal assignment statement is shown as follows:

```

concurrent signal label: conditional_signal_assignment assignment statement ...... -- or label: selected_signal_assignment

```

In Figure 2-21 (lines 9 and 10), a conditional signal assignment performs the signal assignments ( $q \le d1$  or  $q \le d0$ ) based on the conditions defined in the conditional waveform. The format of a conditional signal assignment and the associated conditional waveform is:

conditional signal target <= options conditional\_waveforms; assignment ......

conditional waveforms waveform **when** condition **else**

-- ...

waveform when condition else

waveform

The conditional signal assignment represents a process statement that uses an if statement in the signal transform. The options (**guarded** and **transport**) are not used in the conditional signal assignment in Figure 2-21.

For comparison, the behavioral description of the four-bit shifter from Figure 2-11 is shown again in Figure 2-22 (at the top of the figure) along with the equivalent data-flow description of the same shifter (at the bottom of the figure).

The major difference between the two descriptions is that four process statements are implied in the data-flow description with the four conditional signal assignments (lines 9 through 20). In the behavioral description, one process statement is explicitly called (lines 9 through 20).

The data-flow example in Figure 2-22 uses the same entity declaration and corresponding port clause as the equivalent behavioral description (lines 1 through 5). The architecture body in the data-flow description uses a concurrent signal assignment statement that is composed of four conditional signal assignments; one for each element of the shftout array. This concurrent signal assignment statement does not use the optional label as does the one shown in Figure 2-21, line 8.

```

ENTITY shifter IS --BEHAVIORAL----- entity declaration

1

2

PORT ( shftin : IN bit_vector(0 TO 3); --port clause

shftout : OUT bit_vector(0 TO 3);

3

shftctl : IN bit_vector(0 TO 1) );

5

END shifter;

6

7

ARCHITECTURE behav OF shifter IS -- architecture body

8

BEGIN

9

f2:

--process statement

PROCESS (shftin, shftctl)

10

11

VARIABLE shifted : bit_vector(0 TO 3);--process decl. part

12

BEGIN

13

CASE shftctl IS

--proc. statement part

14

WHEN "00" => shifted := shftin;

15

WHEN "01" => shifted := shftin(1 TO 3) & '0';

16

WHEN "10" => shifted := '0' & shftin(0 to 2);

WHEN "11" => shifted := shftin(0) & shftin(0 TO 2);

17

18

END CASE;

19

shftout <= shifted AFTER 10 ns;</pre>

20

END PROCESS f2;

21

END behav;

ENTITY shifter IS ----- DATA-FLOW---- entity declaration

1

2

PORT ( shftin : IN bit_vector(0 TO 3); -- port clause

3

shftout : OUT bit_vector(0 TO 3);

shftctl : IN bit_vector(0 TO 1) );

4

5

END shifter;

6

7

ARCHITECTURE data_flow OF shifter IS -- architecture body

8

BEGIN

--concurrent sig. assignment

shftout(3) <= '0' AFTER 10 ns WHEN shftctl = "01" ELSE

9

10

shftin(3) AFTER 10 ns WHEN shftctl = "00" ELSE

shftin(2) AFTER 10 ns; -- end cond. sig. assign. 1

11

shftout(2) <= shftin(3) AFTER 10 ns WHEN shftctl = "01" ELSE</pre>

12

13

shftin(2) AFTER 10 ns WHEN shftctl = "00" ELSE

14

shftin(1) AFTER 10 ns; -- end cond. sig. assign. 2

15

shftout(1) <= shftin(2) AFTER 10 ns WHEN shftctl = "01" ELSE

shftin(1) AFTER 10 ns WHEN shftctl = "00" ELSE

16

shftin(0) AFTER 10 ns; -- end cond. sig. assign. 3

17

shftout(0) <= shftin(1) AFTER 10 ns WHEN shftctl = "01" ELSE

18

19

AFTER 10 ns WHEN shftctl = "10" ELSE

20

shftin(0) AFTER 10 ns;--end cond. sig. assign. 4

21

END data_flow;

```

Figure 2-22. Comparison of Behavioral and Data-Flow Shifter Descriptions

#### **Constructs Found in Each Design Description Method**

The following list itemizes the language constructs and functions found in each type of VHDL design description method. The constructs common to all three methods are listed above the dashed line, followed by the constructs that are unique to a particular description method (below the dashed line).

#### **Constructs Common to Structural, Behavioral, and Data-Flow Methods**

| Entity declarations   | Package declarations | Constant declarations |

|-----------------------|----------------------|-----------------------|

| Architecture bodies   | Package bodies       | Subtype declarations  |

| Function declarations | Type declarations    | Concurrent assertions |

| Ports                 | Generics             | Signals               |

| Aliases               | Attributes           | Blocks                |

#### **Constructs Unique to a Particular Design Description Method**

| Structural             | Behavioral                            | Data Flow                |

|------------------------|---------------------------------------|--------------------------|

| Components             | Register and bus signals              | Register and bus signals |

| Config. specifications | Concurrent assignments                | Concurrent assignments   |

| Config. declarations   | Guards                                | Guards                   |

| Generate statement     | Disconnection spec.                   | Disconnection spec.      |

|                        | Procedure declarations                |                          |