# VHDL for ELE548

Heather Hinton<sup>1</sup>

Electrical and Computer Engineering, Ryerson Polytechnic University, 350 Victoria Street, Toronto, Ontario, Canada, M5B 2K3

<sup>&</sup>lt;sup>1</sup> hhinton@ee.ryerson.ca

# **ECE Technical Reports**

This technical report series allows faculty of the Department of Electrical and Computer Engineering to publish detailed and recent research results in a timely manner. It is *not* intended that these technical reports duplicate outside publications. However, due to the time lag in publishing results in formal, peer reviewed venues, many of these technical reports will be submitted for review and publication elsewhere. In such cases, it is intended that the technical reports will contain additional details and results that cannot be included elsewhere due to space limitations.

In addition to technical reports pertaining to research conducted within the Department, the technical report series may also be used to publish "pedagogical" results and methods. Ryerson has a strong tradition and committment to high-quality teaching and teaching methods. Many of our faculty are actively engaged in developing new pedagogical techniques, including the use of multi-media and Web-based tools for instructional purposes. We believe that it is equally important to make these results available to the academic and education community.

While all reports will be numbered sequentially, a research report will be identified by the technical report number and the code  $\mathbf{R}$ . Likewise, a pedagogical report will be identified by the technical report number followed by the code  $\mathbf{P}$ .

For more information about this technical report series, please contact Heather Hinton hhinton@ee.ryerson.ca or Andrew Kennings akenning@ee.ryerson.ca.

# **Publication History**

This manual is an introductory tutorial in VHDL for third year students taking ELE548, Computer Architecture at Ryerson Polytechnic University. Initially, the manual contains only the introductory VHDL tutorial. This manual consists of an introduction to VHDL configured for the course (ELE548), followed by a series of exercises that are to be completed by the student. These exercises are intended to introduce all the concepts required to complete the ELE548 project. The examples used in this document are based the examples discussed in Kevin Skahill's book, "VHDL for Programmable Logic" [1].

©1999 by the authors.

This work may not be copied or reproduced in whole or in part for any commercial purpose. Permission to copy in whole or in part without payment of fee is granted for nonprofit educational and research purposes provided that all such whole or partial copies include the following: a notice that such copying is by permission of the Department of Electrical and Computer Engineering, Ryerson Polytechnic University in Toronto, Canada; an acknowledgement of the authors and individual contributors to the work; an all applicable portions of the copyright notice. Copying, reproducing, or republishing for any other purpose shall require a license with payment of fee to the Department of Electrical and Computer Engineering. All rights reserved.

# Contents

| 1 | Introduction         |                                                  |    |  |  |  |  |

|---|----------------------|--------------------------------------------------|----|--|--|--|--|

|   | 1.1                  | Using VHDL in the Design Process                 | 1  |  |  |  |  |

| 2 | A Simple Circuit     |                                                  |    |  |  |  |  |

|   | 2.1                  | The Entity Declaration                           | 3  |  |  |  |  |

|   | 2.2                  | Architecture Body                                | 4  |  |  |  |  |

|   |                      | 2.2.1 Behavioural Description                    | 4  |  |  |  |  |

|   |                      | 2.2.2 DataFlow Description                       | 5  |  |  |  |  |

|   |                      | 2.2.3 Structural Descriptions                    | 6  |  |  |  |  |

|   | 2.3                  | Signals                                          | 7  |  |  |  |  |

|   |                      | 2.3.1 Internal Signals                           | 7  |  |  |  |  |

|   |                      | 2.3.2 Signal Aliases                             | 8  |  |  |  |  |

|   | 2.4                  | Variables                                        | 8  |  |  |  |  |

| 3 | Con                  | nbinational Logic                                | 9  |  |  |  |  |

|   | 3.1                  | Concurrent Statements                            | 9  |  |  |  |  |

|   |                      | 3.1.1 Boolean Statements                         | 9  |  |  |  |  |

|   |                      | 3.1.2 With-Select-When Statements                | 10 |  |  |  |  |

|   |                      | 3.1.3 With-Select-When-When Others               | 10 |  |  |  |  |

|   |                      | 3.1.4 When-Else Statements                       | 11 |  |  |  |  |

|   | 3.2                  | Sequential Statements                            | 11 |  |  |  |  |

|   |                      | 3.2.1 If-Then-Else Statements                    | 11 |  |  |  |  |

|   |                      | 3.2.2 Case-When Statements                       | 12 |  |  |  |  |

|   |                      | 3.2.3 Loop Statements                            | 12 |  |  |  |  |

| 4 | Synchronous Logic 1- |                                                  |    |  |  |  |  |

|   | 4.1                  | Clocked Circuits                                 | 14 |  |  |  |  |

|   | 4.2                  | Reset Signals                                    | 15 |  |  |  |  |

| 5 | Usi                  | ng Components                                    | 17 |  |  |  |  |

| 6 | Mal                  | king Your Own Library                            | 20 |  |  |  |  |

|   |                      | Component Declaration                            | 20 |  |  |  |  |

|   | 6.2                  | Package Declaration                              | 20 |  |  |  |  |

|   | 6.3                  | Libraries                                        | 21 |  |  |  |  |

|   | 6.4                  | Building Your Library                            | 21 |  |  |  |  |

|   | 6.5                  | Instantiating a Library Component in a VHDL File | 21 |  |  |  |  |

|   | 6.6                  | Compiling Your Library into a VHDL File          | 23 |  |  |  |  |

| 7 | Usi                  | ng Max+PlusII for VHDL                           | 24 |  |  |  |  |

| 8  | VH   | OL Syntax Primer                                      | 25              |

|----|------|-------------------------------------------------------|-----------------|

|    | 8.1  | Reserved Words                                        | 25              |

|    | 8.2  | Declarations                                          | 25              |

|    |      | 8.2.1 Entity Declaration                              | 25              |

|    |      | 8.2.2 Architecture Body                               | 25              |

|    |      | 8.2.3 Library Declarations                            | 26              |

|    |      | 8.2.4 Package Declarations                            | 26              |

|    |      | 8.2.5 Component Declarations                          | 26              |

|    |      | 8.2.6 Signal Declarations                             | 26              |

|    |      | 8.2.7 Constant Declarations                           | 26              |

|    |      | 8.2.8 Alias Declarations                              | 27              |

|    |      | 8.2.9 Variable Declarations                           | 27              |

|    |      | 8.2.10 Integer Type Declarations                      | 27              |

|    | 8.3  | Simple Assignment Statements                          | 27              |

|    | 0.0  | 8.3.1 Signal Assignment                               | 27              |

|    |      | 8.3.2 Variable Assignment                             | 27              |

|    | 8.4  | Concurrent Statements                                 | 27              |

|    | 0.1  | 8.4.1 when-else                                       | 27              |

|    |      | 8.4.2 with-select-when                                | 27              |

|    | 8.5  | Sequential Statements                                 | 28              |

|    | 0.0  | 8.5.1 Process Declaration                             | 28              |

|    |      | 8.5.2 if-then-else                                    | 28              |

|    |      | 8.5.3 case-when                                       | 28              |

|    |      | 8.5.4 for-loop                                        | 28              |

|    |      | 8.5.5 while-loop                                      | 28              |

|    |      | 8.5.6 Synchronous Logic with Asynchronous Reset       | 29              |

|    | 8.6  | Modes                                                 | 29              |

|    | 0.0  | 8.6.1 in                                              | 29              |

|    |      | 8.6.2 out                                             | 29              |

|    |      | 8.6.3 inout                                           | 29              |

|    |      | 8.6.4 buffer                                          | 29              |

|    |      | 0.0.4 Build                                           | 20              |

| 9  | Exe  | cise: A 4-bit Adder                                   | 30              |

|    | 9.1  | A Schematic-Entry 4-Bit Adder                         | 30              |

|    | 9.2  | A VHDL 4-Bit Adder                                    | 30              |

| 10 | Evo  | cise: A 16-bit Adder                                  | 32              |

| ΤÛ |      | Brute Force Schematic Entry 16-bit Adder              | 32<br>32        |

|    |      | Brute Force VHDL 16-bit Adder                         | $\frac{32}{32}$ |

|    |      | 16-bit Adder Using Components                         | $\frac{32}{33}$ |

|    |      | 16-bit Adder Using User-Defined Library Components    | ээ<br>33        |

|    | 10.4 | 10-bit Adder Osing Oser-Denned Library Components     | აა              |

| 11 | Exe  | cise: D Flip-Flops                                    | 35              |

|    | 11.1 | A VHDL Single-Bit D Flip Flop with Asynchronous Reset | 35              |

|    | 11.2 | A VHDL 4-bit D Flip Flop with Asynchronous Reset      | 35              |

| 12 Exercise: Multiplexors                               |      |  |  |  |

|---------------------------------------------------------|------|--|--|--|

| 12.1 A VHDL 2-bit Multiplexor                           | . 37 |  |  |  |

| 13 Exercise: Using Components                           | 38   |  |  |  |

| 13.1 An Adder-D Flip-Flop Circuit                       | . 38 |  |  |  |

| 13.2 Adder-D Flip Flop Circuit Using Library Components | . 39 |  |  |  |

# List of Figures

| Black Box Representation of Circuit                          | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Code: Entity Declaration for Black Box Circuit               | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Code: Declaring and Using Library Packages                   | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Code: Behavioural Description of Black Box Circuit           | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Code: Alternate Behavioural Description of Black Box Circuit | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Code Fragment: DataFlow Description of Black Box Circuit     | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Code: Structure Description of Black Box Circuit             | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Code: Internal Signals                                       | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Code Fragment: Declaring Aliases to a Signal                 | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                              | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Code: Concurrent Boolean Statement Circuit                   | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Code Fragment: With-Select-When Statements                   | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Code: With-Select-When-When Others Statements                | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Code Fragment: When-Else Statements                          | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                              | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                              | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                              | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                              | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                              | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Code Fragment: A Clock-Sensitive Circuit                     | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Code Fragment: A Clocked, Negative-Edge Triggered Circuit    | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                              | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Code: Instantiating A Component                              | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Code: Instantiating Multiple Components                      | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                              | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                              | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Code: Composite Adder-D Flip Flop Circuit                    | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Code: Adder-D Flip Flop Circuit Using Library Components     | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                              | Code: Entity Declaration for Black Box Circuit Code: Declaring and Using Library Packages Code: Behavioural Description of Black Box Circuit Code: Alternate Behavioural Description of Black Box Circuit Code: Alternate Behavioural Description of Black Box Circuit Code: Structure Description of Black Box Circuit Code: Internal Signals Code: Internal Signals Code: Alternate Behavioural Description of Black Box Circuit Code: Concurrent Boolean Statement Circuit Code: Concurrent Boolean Statement Circuit Code: Fragment: With-Select-When Statements Code: With-Select-When-When Others Statements Code: Fragment: When-Else Statements Code Fragment: When-Else Statements Code Fragment: If-Then-Else Statements Code Fragment: Case-When Statements Code: For-Loop Statements Code: For-Loop Statements Code: While-Loop Statements Code: While-Loop Statements Code: While-Loop Statements Code Fragment: A Clock-Sensitive Circuit Code Fragment: A Synchronous Resets in Synchronous Circuits Code: Instantiating A Component Code: Instantiating Multiple Components Code: User-Defined Libraries and Components Code: Composite Adder-D Flip Flop Circuit |

### 1 Introduction

VHDL is an acronym for Very High-Speed-Integrated-Circuit Description Language, which pretty much describes what VHDL actually is. It is a language, just as C and Java are languages. VHDL is used to describe, model, and synthesize (make) a circuit, just as C is used to describe, model and implement a solution to a problem. So, don't be surprised when we refer to your VHDL solutions as "code"!

Like C, VHDL supports libraries (design libraries that contain common or reusable components, such as **and** gates). VHDL also allows us to create modular designs, so that we can take advantage of hierarchical design (building a big, complex circuit from a bunch of smaller, simpler circuits).

Like Java, VHDL is "device independent". That is, we can design a circuit before we know which type of device it will be implemented on. In fact, we can take the same design and "target" many different device architectures.

Once you have designed a circuit, there are two main tasks that you can accomplish: you can *synthesized* the circuit or you can *simulate* the circuit. Simulation is usually done before synthesis. In ELE548 we will focus on simulation. Why? By simulating a VHDL design of a circuit, we can "run" the VHDL code and determine if their are flaws that will prevent the actual realization of the circuit from working. Simulation is a way to test a hardware circuit in software, before we go through the time and expense of implementing the hardware.

There is a danger with relying only on simulation, however. In software, we can design a circuit that cannot be easily realized (synthesize) in hardware. Indeed we can (inadvertently, of course) design a circuit that is physically meaningless! For this reason, we will (try very hard to have the equipment to allow you to) synthesize and implement a VHDL design at the end of this course.

# 1.1 Using VHDL in the Design Process

In general, there is a recipe of steps to follow when designing a circuit. These steps can be described as (p. 8, [1]):

- 1. Define the design requirements

- 2. Define (code) the design in VHDL

- 3. Simulate the VHDL "source" code

- 4. Synthesize the design <sup>1</sup>

- 5. Fit the design into a given device architecture

- 6. Programme the device

<sup>&</sup>lt;sup>1</sup>At the same time we may also *optimize* the design, so that it will perform better for a given device architecture. We will probably also concern ourselves with *placing* and *routing* the design, that is, making the VHDL design fit within the constraints of a programmable logic device or a field-programmable gate array.

In this course we will stick to steps 1, 2, and 3. That will be plenty for our purposes, especially because steps 2 and 3 are often iterative (again, like C, there will be debugging, but no hacking).

**Note:** This tutorial should provide you with the background information you need to complete the ELE548 project. There are several other good sources of VHDL information that you may wish to investigate, including

- The Max+plusII VHDL Help (Help Menu, VHDL Help) has lots of information, including a syntax definition, information on templates and how to use the VHDL compiler within Max+plusII.

- Keven Skahill's book, VHDL for Programming Logic, [1], is also very good, but at a bit higher level than required for this course. Nevertheless, a good reference and may be handy for later courses. This is Prof. Hinton's favourite VHDL reference.

- The book by Charles Roth, [2], Digital Systems Design Using VHDL is another good reference book that happens to be Prof. Kennings' favourite. This book is more "textbook-like" then the Skahill book.

# 2 A Simple Circuit

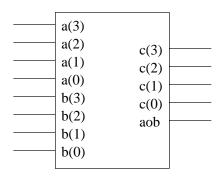

To make our VHDL design as modular as possible (so that we can take advantage of the benefits of hierarchical design), VHDL forces us to keep the circuit interface and internals separate. Consider a black box, shown in Figure 1, that takes as input two four-bit vectors and produces a four-bit vector output. We know nothing about how the input or the output are related and what the functionality of this black box actually accomplishes. But, we do know a great deal about the interface to this black box. If we think about this black box as a C-function, what we know from this figure is the equivalent of the function declaration, called the **entity declaration** in VHDL.

Figure 1: Black Box Representation of Circuit

# 2.1 The Entity Declaration

In VHDL, we describe the interface to this black box/entity using an **entity declaration**, as shown in Figure 2. Like a function declaration in C, an entity declaration describes the inputs and outputs to an entity (the black box). This entity has two inputs, the four-bit vectors **a** and **b**, and two outputs, a four-bit vector **c** and a single bit output **aob**. The entity has the name **bbox**, and the definition of the entity is *bounded* by the **entity bbox** and **end bbox** statements.

```

entity bbox is port(

a,b : in std_logic_vector(3 downto 0);

c : out std_logic_vector(3 downto 0);

aob : out std_logic);

end bbox;

```

Figure 2: Code: Entity Declaration for Black Box Circuit

The words entity, is, port, end, in, out, std\_logic, std\_logic\_vector, and downto are reserved words in VHDL, meaning that the VHDL compiler knows what these words mean and you cannot use them as variable names.

What is a **port**? It is an I/O signal within an entity declaration. In the code shown above, there are four ports. Each port is declared with a **signal name** (such as **a** or **aob**), a **mode** (or direction, such as **in** or **out**), and a **data type** (such as **std\_logic\_vector**).

The code above shows two types of mode in the entity declaration, **in** and **out**. These can be thought of as "single-use" or "unidirectional" modes: the source of an in-mode signal is external to the entity, and the destination of an out-mode signal is external to the entity.

An additional, useful, mode is the **inout** mode. This mode is used to declare a signal that acts as both an input and an output signal (think of feedback).

All we know about the inside of the black box from the mode description is which signals are used as inputs and which signals are used as outputs. The data types of a port declaration tells us how to treat the signal on the port. Just as in C, declaring a variable as an integer or a floating point tells us how to interpret the variable, declaring a port with a data type tells us how to interpret the data on the port. So, **std\_logic\_vector(3 downto 0)** describes a four-bit vector (bits 0, 1, 2, 3) where the order of significance is from bit(3) downto bit(0). **std\_logic** without the vector qualifier describes a single bit.

The **std\_logic** type is an IEEE standard, provided by the IEEE std\_logic\_1164 package. In order to use this library, we must include it (remember including library files in C?). We include the library and the packages used *before* the entity declaration, as shown in Figure 3.

```

library ieee;

use ieee.std_logic_1164.all;

entity entity_name is port(

-- stuff missing here

end entity_name;

```

Figure 3: Code: Declaring and Using Library Packages

The words **library** and **use** are also reserved words in VHDL. Also, the **ieee** library is "built-in" to VHDL (remember how C knows about system include files?).

# 2.2 Architecture Body

What about the internal workings of the entity? We know what the entity interface looks like, thanks to the entity declaration. We must now define the **architecture body**, the internal working, or behaviour, of the entity. We can chose between one of three "ways" to describe the architecture body: behavioural, dataflow, or structural descriptions. The main difference between these approaches is the level of detail required (or, conversely, the level of abstraction allowed).

### 2.2.1 Behavioural Description

Consider the architecture body shown in Figure 4. This behaviour description is quite reminiscent of a C-language programme in many ways. Behavioural descriptions are high-level, just as C is a high-level language. The architectural description is bounded by the **architecture** and **end arch\_bbox** statements. When declaring the **architecture arch\_bbox**, we define which entity the architecture belongs to (**of** bbox **is**). The **process** statement is used to enclose an algorithm.

The process in Figure 4 is named **comp** and the **sensitivity list** of comp is declared as (a,b). The sensitivity list identifies the signals that will cause the process to execute. In this

```

architecture arch_bbox of bbox is

begin

comp: process (a,b) begin

c <= b;

if a = b then

aob <= '1';

else

aob <= '0';

end if

end process comp;

end arch_bbox;</pre>

```

Figure 4: Code: Behavioural Description of Black Box Circuit

```

architecture arch_bbox of bbox is

begin

comp: process (a,b) begin

c <= b;

aob <= '0';

if a = b then

aob <= '1';

end if

end process comp;

end arch bbox;</pre>

```

Figure 5: Code: Alternate Behavioural Description of Black Box Circuit

case, the circuit is sensitive to changes in the two input signals, **a** and **b**. This means that whenever **a** or **b** changes, the **comp** process changes.

Note that the assignment statement **aob** <= '1' indicates that the variable **aob** is assigned the (bit) '1'. To see how this reads, try reading this statement from right to left, instead of the usual left to right. You can then pronounce this statement as '1' is assigned to **aob**.

Why is this description called behavioural? Because it is fairly easy to read the behaviour from the description: this VHDL listing describes a 4-bit equality comparison function. Because this behavioural description is given by an algorithm, we may suspect, that like a high-level programme written in C, this is not the only possible description. So, the VHDL code shown in Figure 5 is equivalent to the code shown in Figure 4.

### 2.2.2 DataFlow Description

A dataflow description is very similar to a behavioural description. In fact, the two are often both referred to as behavioural. The main difference is that a dataflow description does not use the **process** construct. Clearly the dataflow description is easy to understand for a simple example, such as the one we are looking at. With a more complicated algorithm

```

architecture dataflow of bbox is

begin

aob <= '1' when (a=b) else '0';

end dataflow;</pre>

```

Figure 6: Code Fragment: DataFlow Description of Black Box Circuit

is required, such as one with nested sequential statements, a behavioural description will probably make more sense.

The big difference between behavioural and dataflow can be seen when we consider a circuit where the inputs may change at any time, but where we only want these (possibly changed) inputs to be noticed when a clock pulse triggers the circuit. We can easily describe this using a behavioural description where **process(clk)** identifies the clock signal as causing the circuit to activate <sup>2</sup>. With a dataflow description, we cannot as easily or neatly control "when" the circuit activates.

### 2.2.3 Structural Descriptions

A structural description consists of VHDL **netlists**, lists of signals and how they are "joined" by components, such as **and** or the hierarchically created **xnor** (a combination of **nor** and **not**).

```

use work.gatespkg.all;

architecture struct of bbox is

signal tmp : std_logic_vector(0 to 3);

begin

u0: xnor2 port map (a(0),b(0),tmp(0));

u1: xnor2 port map (a(1),b(1),tmp(1));

u2: xnor2 port map (a(2),b(2),tmp(2));

u3: xnor2 port map (a(3),b(2),tmp(3));

u4: and4 port map (tmp(0),tmp(1),tmp(2),tmp(3),aob);

end struct;

```

Figure 7: Code: Structure Description of Black Box Circuit

Take a look at the code shown in Figure 7. This is the structural equivalent of the behavioural and dataflow descriptions already discussed. The netlists in this description relate the inputs  $\mathbf{a(1)}$  and  $\mathbf{b(1)}$  with the output  $\mathbf{tmp(1)}$  using the component  $\mathbf{xnor2}^3$ . Netlists are not as easy to read or understand as the behavioural or dataflow descriptions we have already seen. For this reason, we will focus on behavioural and/or dataflow descriptions in this course.

<sup>&</sup>lt;sup>2</sup>See the section on clocked circuits for more details.

<sup>&</sup>lt;sup>3</sup>The components **xnor2** and **and4** must have been defined elsewhere, and compiled into the library **work.gatespkg.all**. This allows us to create our **bbox** component hierarchically, building on already defined components. If we compile **bbox** and include it in a library, it to can be used to hierarchically create more complex components. We will see how to do this in one of the exercises.

### 2.3 Signals

So far, we have focused on input and output signals defined in an entity declaration. These signals define the interface to the circuit that we are designing. These signals may have the "directions" (or modes) of **in**, **out**, or **inout** <sup>4</sup>. Other useful signals include internal signals (discussed in next section), signal aliases (following next section) and clock and reset signals (both synchronous and asynchronous), discussed in Section 4.1.

```

library work;

use work.gatespkg.all;

entity bbox is port(

a, b : in std_logic_vector(3 downto 0);

axnorb : out std_logic);

end bbox;

architecture struct of bbox is

signal tmp : std_logic_vector(0 to 3);

signal out_and4 : std_logic;

begin

-- instantiate components

u0: xnor2 port map (a(0),b(0),tmp(0));

u1: xnor2 port map (a(1),b(1),tmp(1));

u2: xnor2 port map (a(2),b(2),tmp(2));

u3: xnor2 port map (a(3),b(2),tmp(3));

u4: and4 port map (tmp(0), tmp(1), tmp(2), tmp(3), out_and4);

-- extract output signal

axnorb <= int_out_and4;</pre>

end struct;

```

Figure 8: Code: Internal Signals

#### 2.3.1 Internal Signals

In section 2.2.3, we saw a signal defined in the architecture body that did not have a **mode** (signal **tmp**). This signal is an *internal* signal, meaning that it is not part of the interface defined in the entity declaration. Internal signals are very useful as they provide a means of "gluing" components together. In Figure 7, the internal signal **tmp** is used to glue the outputs of the **xnor** components to the input of the 4-input **and4** component.

In fact, we can also use internal signals to define the output of the **and4** component. If we do this, however, we must find a way to *extract* this internal signal, and map it to an interface signal (defined as mode **out** in the entity declaration). This is actually quite easy, and is shown in Figure 8.

<sup>&</sup>lt;sup>4</sup>Additionally, these signals could be defined as **buffer**, although we will not discuss this mode in this course.

### 2.3.2 Signal Aliases

Another useful thing that we can do is create a signal **alias**. Aliases are useful for allowing us to rename a signal, perhaps into a more meaningful signal name, for the scope of a description. The declaration of an alias is shown in Figure 9.

```

signal input_vector: std_logic_vector(15 downto 0);

alias op_vector: std_logic_vector(7 downto 0) is input_vector(15 downto 8);

alias op1 : std_logic_vector(3 downto 0) is input_vector(7 downto 4);

alias op2 : std_logic is input_vector(3);

```

Figure 9: Code Fragment: Declaring Aliases to a Signal

An alias is an "alternative identifier" for an existing object. A change to an alias is equivalent to a change to the original signal. For example, assigning a value to **op2** in Figure 9 has the same affect as assigning that value to **input\_vector(3)**.

Aliases are really useful if you have a vector signal, where individual bits within the vector have distinct meanings. Using an alias, we can create an identifier to refer to these bits individually.

### 2.4 Variables

How do we store local values in VHDL? A signal doesn't really allow us to do this. Instead, we resort to **variables**, declared as follows:

```

variable var_name : var_type := var_initial_value;

```

Variables must be declared in a process, and are local to that process (recall that signals, on the other hand, are defined *outside* of a process).

```

architecture arch_bbox of bbox is

begin

comp: process (a,b)

variable inc_amt: integer := 2

begin

-- code that includes use of integer variable inc_amt

end process comp;

end arch_bbox;

```

Figure 10: Code: Alternate Behavioural Description of Black Box Circuit

Useful variable types that you may require in this course include **bit**, **boolean**, and **integer**

If you need a variable with a constant value, you can declare a **constant**:

```

constant constant_name : const_type := const_initial_value;

```

The constant types are the same as the variable types. Like a variable, a constant must be declared within a process and is local to that process.

# 3 Combinational Logic

Combinational logic can be written with both *concurrent* and *sequential* statements. Concurrent statements may be executed in parallel (concurrently) and are found in dataflow and structural descriptions of a circuit. Sequential statements must be executed in a given sequential order and are used in behavioural descriptions (hint: what is the big difference between behavioural and dataflow descriptions?)

### 3.1 Concurrent Statements

Concurrent statements fall outside of the process statement (and hence fit nicely with dataflow descriptions).

#### 3.1.1 Boolean Statements

The most "obvious" of concurrent statements are boolean statements. As an example, suppose we wish to build a circuit that will produce the logical-and and logical-or of two bits. We can accomplish this using boolean statements, as shown in Figure 11.

```

library ieee;

use ieee.std_logic_1164.all;

entity cct1 is port(

a,b : in std_logic;

land,lor : out std_logic);

end cct1;

architecture archcct1 of cct1 is

begin

land <= a and b;

lor <= a or b;

end archcct1;</pre>

```

Figure 11: Code: Concurrent Boolean Statement Circuit

The output of this circuit is the two signals, **land** and **lor**, produced concurrently (simultaneously).

The boolean statements that are available in the ieee 1164 library are:

```

and, or, nand, not, xor, xnor

```

These data types can be used with bit and Boolean variables (std\_logic) and with one-dimensional arrays of bits and Boolean variables (such as std\_logic\_vector(3 downto 0)), where both variables have the same length.

If you have an equation with multiple boolean operations, you must use parenthesis to force VHDL into order of operations (otherwise you will get a compile-time error).

#### 3.1.2 With-Select-When Statements

There may be cases where a signal value is assigned based on the value of another signal (a selection signal). In this case, the with-select-when statements come in handy.

For example, consider a circuit where the output,  $\mathbf{z}$ , will be assigned the value of signals  $\mathbf{a}$  or  $\mathbf{b}$ , depending on the value of a selection signal,  $\mathbf{s}$ . We can represent this in VHDL as shown in Figure 12.

Figure 12: Code Fragment: With-Select-When Statements

Careful inspection of this code fragment should convince you that it is remarkably similar to the circuit that you designed in the "Introduction to Max+plusII" tutorial. In fact, we have used the with-select-when statement to implement a single-bit multiplexor. **Note:** What happens if you put this code fragment into a proper VHDL structure and try to compile it? To see why this happens, read the next section... This example is easily expanded to create higher-order multiplexors.

### 3.1.3 With-Select-When-When Others

Because of how **std\_logic** is defined, a single bit does not necessarily have only two values (unless it is explicitly **Boolean**). Other possible values include high impedance, unspecified, low impedance, and so on. For this reason, we have the choice of specifying the case **when others** as a catch-all for all other, not already specified, values of the selection signal. This idea is similar to the use of **default** in a C-language **case** statement.

Figure 13 shows the **when-others** "equivalent" of Figure 12.

```

ARCHITECTURE cct OF testcct IS

BEGIN

with s select

z <= a when '0',

b when '1',

'0' when others;

```

Figure 13: Code: With-Select-When-When Others Statements

The code in Figure 13 states that for *any* value of  $\mathbf{s}$  other than " $\mathbf{0}$ ", the signal  $\mathbf{z}$  will have the same value as the signal  $\mathbf{b}$ .

#### 3.1.4 When-Else Statements

The **when-else** statements are a version of the **when-select** statements where assignment is based on a condition that may or may not revolve around a single signal. The condition evaluated in this type of statement may be based on a single signal, like the **when-else** statements, or on multiple signals, or multiple conditions involving different signals. For this reason, there is an order of preference within a **when-else** statement; once a successful, or true, condition is encountered, the assignment specified by the **when-else** statement is executed and the entire clause is "exited".

For example, the **when-else** equivalent of the code of Figures 12 and 13 is shown in Figure 14.

Figure 14: Code Fragment: When-Else Statements

Suppose we only want **z** to be assigned the value of **a** or **b** based on the select signal **s** and some other condition. We can create compound conditional statements within a **when-else** statement. All that we have to do enclose the compound statement in a set of parentheses, to "create" a simple statement, as seen in Figure 15.

```

ARCHITECTURE cct OF testcct IS

BEGIN

z <= a when (s='0' and ocond1=true) else

b when (s='1' and ocond2=true) else

z;

END cct;

```

Figure 15: Code Fragment: When-Else Statements

## 3.2 Sequential Statements

The combinational circuit(s) that we saw in the previous sections were fairly simple: they could be implemented using simple gate logic, and represented with simple combinational expressions.

In this section, we will look at sequential statements, those that are used within behavioural descriptions.

### 3.2.1 If-Then-Else Statements

The **if-then-else** statements have the same meaning in VHDL as they do in the C-language. By comparison with the combinational statements of the previous section, these statements

are the sequential equivalents of the with-select-when and when-else statements.

Figure 16 represents the **if-then-else** equivalent representation of the multiplexor-type functionality described in the previous section.

```

ARCHITECTURE cct OF testcct IS

BEGIN

test: process(a,b,s)

begin

if s='0' then

z <= a;

elsif (s='1') then

z <= b;

end if;

end process;

END cct;

```

Figure 16: Code Fragment: If-Then-Else Statements

#### 3.2.2 Case-When Statements

A case-when statement is the sequential equivalent of a with-select-when statement. Figure 17 shows the case-when equivalent of the simple, single-bit multiplexor-type circuit of Figures 12 to 16. Note that this code must account for the other possible values of the signal s.

```

ARCHITECTURE cct OF testcct IS

BEGIN

test: process(s)

begin

case s is

when '0' => z <= a;

when '1' => z <= b;

when others => z <= b;

end case;

end process;</pre>

```

Figure 17: Code Fragment: Case-When Statements

### 3.2.3 Loop Statements

There are two types of loop statements that we can use in VHDL: a **for** loop and a **while** loop. They tend to be used when a set of repetitive operations need to be executed, usually a bit-wise operation on a bit-vector. Figure 18 shows a simple **for-loop** used to initialize an 8-bit vector.

```

ARCHITECTURE cct OF test_cct IS

signal sum: std_logic_vector(7 downto 0);

BEGIN

test: process(clk)

begin

for i in 7 downto 0 loop

sum(i) <= '0';

end loop;

-- code requiring clk and sum

end process;

END cct;</pre>

```

Figure 18: Code: For-Loop Statements

Unlike a **for-loop**, which has a predefined number of iterations, controlled by the counter (**i** in Figure 18), a **while-loop** will execute as long as a "controlling" condition evaluates to true (just like in the C-programming language) <sup>5</sup>. The **while-loop** equivalent of Figure 18

```

ARCHITECTURE cct OF test_cct IS

signal sum: std_logic_vector(7 downto 0);

BEGIN

test: process(clk)

variable i: integer := 0;

begin

while i < 7 loop

sum(i) <= '0';

i = i+1;

end loop;

...

end process;</pre>

```

Figure 19: Code: While-Loop Statements

is shown in Figure 19.

Note that the **while-loop** of Figure 19 requires that we declare and initialize the variable **i**. Again, we can see the similarities to the C-language, where **i** is local to the scope of a **for** loop and need not be declared, but is not "built-in" to a **while** loop and therefore must be declared and initialized.

<sup>&</sup>lt;sup>5</sup>Note that this construct is *not* supported by Max+PlusII.

# 4 Synchronous Logic

What happens when we need to synchronize our actions, for example, when a circuit is clocked? It shouldn't be too surprising to realize that a dataflow description does not handle synchronous logic well: this is due in large part to the lack of a **process** statement in a dataflow description.

### 4.1 Clocked Circuits

A **process** statement easily handles synchronous logic, by allowing us to specify a clock signal as one of the triggers to the circuit. Figure 20 shows a circuit that is sensitive *only* to changes in the clock signal.

```

ARCHITECTURE cct OF testing IS

BEGIN

process (clk)

begin

...

end process;

END cct;

```

Figure 20: Code Fragment: A Clock-Sensitive Circuit

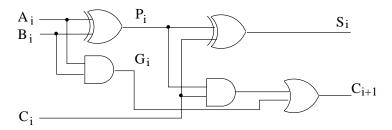

Let's think about what a clock signal, or any waveform for that matter, looks like. There will be a rising edge and a falling edge. Do we want our circuit to be triggered by any change in the clock signal, or {positive,negative} edge-triggered? How do we represent edge-triggering in VHDL?

Edge-triggering requires two conditions to be true: 1) the clock signal must change, and 2) it must change in the positive (negative) direction, as required. Representing edge-triggering in VHDL therefore requires a compound statement, specifying each of these conditions.

To represent the change in a clock signal, we need some way to record or recognize that an event (corresponding to the change in clock value) has occurred. To do this, we consider the **event attribute** of the clock signal, given by **clk'event** <sup>6</sup>.

Unfortunately, all that the **clk'event** attribute tells us is that we have encountered an edge in the clock signal, and not whether it was a rising or falling edge. To further specify the type of edge encountered, we also specify the value of the clock after the edge has "completed". Thus a value of **clk='1'** would indicate that a rising edge had just occurred, and a value of **clk='0'** would indicate that a falling edge had just occurred.

Figure 21 shows the clock-sensitive circuit of Figure 20 re-written to specify a negative-edge triggered circuit.

<sup>&</sup>lt;sup>6</sup>See the subsection on Attributes at the end of this section.

```

ARCHITECTURE cct OF testing IS

BEGIN

process (clk) begin

if (clk'event and clk='0') then

...

end if;

end process;

END cct;

```

Figure 21: Code Fragment: A Clocked, Negative-Edge Triggered Circuit

### 4.2 Reset Signals

Resets are a generally very useful thing. A reset signal in a circuit can be used to restore initial conditions, such as resetting a counter to its initial count value. The problem with resets is that they are generally asynchronous signals. How do we work a reset into an synchronous circuit?

This is actually quite easy if we remember a couple of things about VHDL. The first is that we can specify in the process sensitivity a list of all signals that affect the circuit outputs. So, we can specify a sensitivity list that includes both the (synchronous) clock signal and the (asynchronous) reset signal.

The second thing that we must remember that in the specification of a sequential statement such as an **if-then-else** statement, there is an order of preference that is followed. The first conditions that are encountered are of higher precedence, even if subsequent conditions are also true. So, as long as the **reset** conditions are tested first, we should be okay.

Figure 22 shows how to incorporate an asynchronous reset signal into a synchronous circuit. The sensitivity list tells us that the circuit outputs are sensitive to changes in the **clk** signal and the **reset** signal. The first condition included in the **if** statement concerns the **reset** signal; if this (asynchronous) signal is set, then the reset actions will be executed. If the (asynchronous) **reset** signal is *not* set, and the **rising edge** of the clock has occurred (note that **rising\_edge** == (**clk'event** and **clk='1'**)) then the synchronous rising edge triggered actions occur.

```

ARCHITECTURE cct OF testing IS

BEGIN

process (clk, reset) begin

if (reset = '1') then

-- do (asynch) reset actions

elsif rising_edge(clk) then

-- do (synch) rising edge clock triggered actions

end if;

end process;

END cct;

```

Figure 22: Code Fragment: Asynchronous Resets in Synchronous Circuits

#### Attributes

In VHDL, we often need to consider some **attribute** of a signal, such as recognizing when a signal changes. When a signal changes, an event is said to have occurred; we recognize this by looking at the **event attribute** of a signal <sup>7</sup>.

An attribute is simply a (predefined) means of providing information about an item. An attribute is represented with a tick-mark ' and the attribute-reserved word. The attribute that identifies that a signal has changed is given as 'event. If we wish to specify that a given signal, for example, the clock, has changed, we can write:

#### clk'event

The value of **clk'event** is false, unless an event has just occurred (the clock has changed value) when **clk'event** will be true.